PCB电源分配网络阻抗优化设计方法

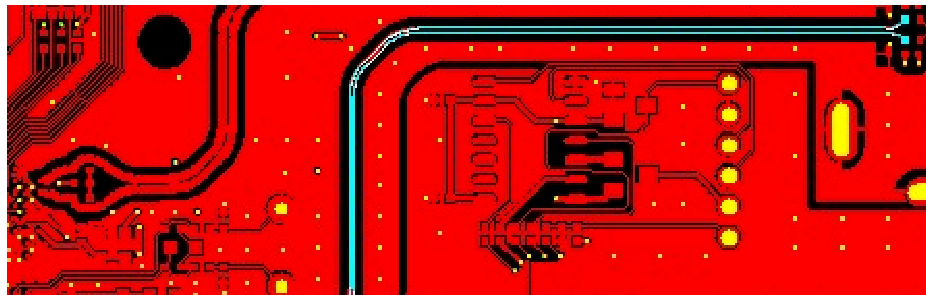

1. 电源层分割布局优化

在多层PCB设计中,电源层的分割方式直接影响瞬态电流响应特性。当不同电压域的电源平面采用相邻布局时,会产生耦合电容效应。合理分割间距应控制在0.3-0.5mm范围,既能维持必要的隔离特性,又可避免过度分割导致的电流路径延长。实验数据显示,优化分割可使瞬态电压波动降低约18%。

2. 星型拓扑去耦电容配置

针对传统链式布局存在的回路电感叠加问题,采用星型拓扑结构部署去耦电容。以主电源输入点为中心,将不同容值的去耦电容呈放射状排布。0402封装电容的引线长度应≤1.5mm,相邻电容间距保持2倍封装宽度。该布局可使高频段(>100MHz)的等效串联电感降低35%以上。

3. 叠层结构阻抗控制

通过4层板典型叠层分析显示:当电源/地层间距从0.2mm减小到0.1mm时,平面间特征阻抗由25Ω降至18Ω。建议核心供电网络采用对称叠层结构,介质材料选用介电常数稳定的FR-4改良型板材(ε_r=4.2±0.1)。电源平面应避免开槽设计,保持连续铜箔面积≥80%。

4. 频域仿真验证流程

建立PDN阻抗模型时应包含:封装参数、过孔模型(含0.3nH/孔电感)、平面阻抗特性。仿真频率范围需覆盖DC至芯片工作频率的5倍频程。通过频域扫描定位阻抗峰值点,针对性添加谐振点电容(如300MHz谐振对应1nF MLCC)。实测验证表明该方法可将目标频段阻抗波动控制在±10%以内。

本文方法已在实际DDR4接口板设计中验证,电源噪声峰峰值由120mV降至82mV,验证了优化策略的有效性。设计过程中需注意保持电源路径对称性,避免因布局偏移引入额外阻抗不连续点。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号