阻焊层厚度:高频PCB信号完整性指南

在高频 PCB 设计领域,每个细节都很重要。影响信号完整性的一个经常被忽视的因素是阻焊层厚度。对于精度至关重要的射频电路,阻焊层的厚度及其介电常数直接影响信号损耗、阻抗控制和整体性能。那么,阻焊层厚度如何影响高频 PCB,为什么要关心呢?简而言之,精心选择的阻焊层厚度可确保最小的信号损失并保持阻抗,这对于可靠的射频性能至关重要。

什么是阻焊层,为什么它在高频 PCB 中很重要?

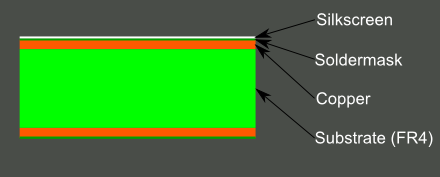

阻焊层是涂在印刷电路板 (PCB) 铜迹线上的一层薄保护层。它的主要工作是通过绝缘走线并保护它们免受湿气和灰尘等环境因素的影响来防止短路。它还通过确保焊料仅粘在指定的焊盘上来帮助焊接。虽然这些功能对于任何 PCB 都至关重要,但阻焊层在高频设计(例如射频电路中使用的设计)中发挥着更为关键的作用。

在高频 PCB 设计中,信号以令人难以置信的速度传播,通常在千兆赫 (GHz) 范围内。在这些频率下,即使是材料或尺寸的微小变化也会破坏信号完整性。阻焊层虽然很薄,但直接位于铜迹线上或铜迹线附近,影响其周围的电磁场。如果管理不当,其厚度和介电特性会改变信号的传播方式,从而导致信号丢失或阻抗不匹配等潜在问题。

阻焊层厚度在信号完整性中的作用

信号完整性是指电信号在电路中传播时的质量和可靠性。在高频 PCB 中,由于串扰、噪声和信号丢失等因素,保持信号完整性是一项挑战。阻焊层厚度在这个等式中起着令人惊讶的重要作用。

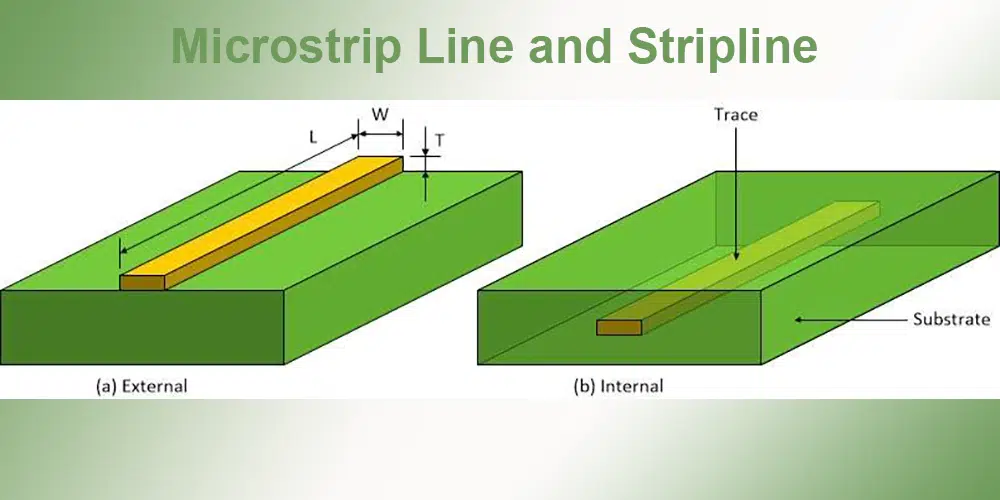

在设计射频电路时,工程师通常以受控阻抗为目标——对于大多数射频应用来说,阻抗通常为 50 欧姆。阻焊层是一种介电材料,会影响走线与周围环境之间的电容。较厚的阻焊层会增加电容,从而降低走线的阻抗。相反,较薄的阻焊层会降低电容,从而可能提高阻抗。如果不加以考虑,可能会导致不匹配,导致反射并降低信号质量。

例如,0.8 至 1.2 密耳(20-30 微米)的标准阻焊层厚度可能适用于低频设计。然而,在工作频率为 5 GHz 或更高的射频电路中,即使是 0.2 mil 的变化也会使阻抗偏移 1-2 欧姆,足以导致明显的信号衰减。这就是为什么精确控制射频电路的阻焊层厚度至关重要。

阻焊层介电常数及其对信号损耗的影响

除了厚度之外,阻焊层介电常数(通常表示为 Dk)是高频 PCB 设计中的另一个关键因素。介电常数衡量材料在电场中存储电能的能力。对于阻焊层,Dk 通常在 3.5 到 4.5 之间,具体取决于材料和制造商规格。

较高的介电常数意味着阻焊层可以存储更多的能量,这会减慢信号速度并增加阻焊层导致信号丢失的风险。这种损耗通常称为介电损耗,在较高频率下变得更加明显。例如,在 10 GHz 时,Dk 为 4.0 的阻焊层可能会导致每英寸 0.02 dB 的信号损耗,而在相同条件下,较低的 Dk 为 3.5 可能会将该损耗降低 20-30%。

选择介电常数较低的阻焊层有助于最大限度地减少信号损失,但通常成本较高。此外,掩模的厚度与其 Dk 相互作用。具有高 Dk 的较厚掩模会放大介电损耗,而较薄的掩模可以减轻其中一些影响。平衡这些因素是优化射频性能的关键部分。

射频电路的最佳阻焊层厚度

那么,射频电路的理想阻焊层厚度是多少?答案取决于您设计的具体要求,包括工作频率、走线几何形状和阻抗目标。但是,一般准则可以帮助您朝着正确的方向前进。

对于大多数高频应用,通常建议使用 0.5 至 0.8 密耳(12-20 微米)的阻焊层厚度。该范围在提供足够的保护和最大限度地减少对信号完整性的影响之间取得了平衡。更薄的模板可降低电容和介电损耗,这有利于工作频率高于 1 GHz 的射频信号。然而,太薄(低于 0.5 密耳)可能会损害口罩的保护能力,从而在处理或组装过程中损坏迹线。

在某些情况下,设计人员选择从关键的射频走线上完全去除阻焊层,从而暴露裸铜。虽然这消除了掩模引起的介电损耗和阻抗变化,但它会留下容易氧化和环境破坏的痕迹。如果使用裸迹线,通常会使用像 ENIG(化学镀镍浸金)这样的表面光洁度进行保护,尽管这引入了在阻抗计算中需要考虑的一组变量。

阻焊层引起的信号损失:如何将其最小化

如前所述,阻焊层引起的信号损失是高频 PCB 设计中的一个重要问题。这种损耗主要通过两种机制发生:介电损耗(由于掩模的材料特性)和导体损耗(受掩模与走线相互作用的影响)。以下是最大限度地减少这些影响的一些实际步骤:

选择低损耗材料:选择介电常数和耗散因数 (Df) 较低的阻焊材料。低于 0.02 的 Df 是射频应用的理想选择,因为它表明能量损失较低。

控制厚度:与您的 PCB 制造商合作,确保阻焊层厚度一致,在 RF 设计的最佳范围内 0.5-0.8 密耳。

部分掩蔽:考虑仅将阻焊层应用于非关键区域,如果需要保护,则将射频迹线暴露在外或用最小层覆盖。

模拟和测试:在制造之前使用仿真工具对阻焊层对信号损失的影响进行建模。电磁场求解器等工具可以预测不同的厚度和材料如何影响目标频率下的性能。

通过采取这些步骤,您可以显着减少信号衰减并确保您的高频 PCB 按预期运行。

高频设计中带阻焊层的阻抗控制

阻焊层阻抗控制是成功高频 PCB 设计的基石。当信号沿着走线传播时,它们会遇到由走线宽度、基板高度、基板介电常数以及阻焊层决定的特性阻抗。阻抗不匹配会导致信号反射,从而使波形失真并降低性能。

对于标准FR-4基板(Dk为4.4)上的典型50欧姆微带线,由于电容增加,阻焊层厚度为1mil可能会降低1-3欧姆。虽然这看起来很小,但即使是很小的偏差也会在需要严格公差的射频系统中引起问题。要通过阻焊层实现精确的阻抗控制,请考虑以下事项:

调整跟踪几何体:如果不可避免地使用较厚的阻焊层,您可以通过稍微加宽走线或调整基板高度来保持所需的阻抗来进行补偿。

使用仿真软件:场求解器等工具可以帮助计算阻焊层厚度对阻抗的确切影响,从而实现微调设计。

指定公差:与您的 PCB 制造商沟通,以确保严格控制阻焊层应用,指定目标厚度和可接受的变化(例如±,0.1 密耳)。

使用阻焊层进行高频 PCB 设计的挑战

高频 PCB 设计面临着独特的挑战,而阻焊层往往是这些问题的核心。一个常见的问题是口罩应用不一致。全面厚度的变化会导致阻抗不均匀和信号丢失,尤其是在大型或复杂的设计中。与能够保证均匀应用的可靠制造商合作至关重要。

另一个挑战是保护和性能之间的权衡。虽然较厚的阻焊层可提供更好的绝缘性和耐用性,但它会增加介电损耗并改变阻抗。另一方面,更薄的掩模或根本不戴掩模可以提高电气性能,但会留下易受攻击的痕迹。找到适当的平衡通常需要迭代测试并与制造团队密切合作。

为从事射频 PCB 工作的工程师提供的实用技巧

如果您正在深入研究高频 PCB 设计,这里有一些可行的技巧可以优化阻焊层的使用,从而获得更好的信号完整性:

尽早协作:在设计阶段与您的 PCB 制造商合作,了解他们的阻焊层功能和材料选项。

优先考虑低 DK 材料:对于 4.0 GHz 以上的频率,投资介电常数低于 5 的阻焊材料,以最大限度地减少信号损失。

文件规格:在设计文件中明确定义阻焊层厚度和公差,以避免生产过程中出现意外情况。

测试原型:构建和测试原型以验证您的设计假设,尤其是在您突破频率限制或使用非常规叠层时。

这些步骤可以节省时间和资源,同时确保您的射频电路在实际条件下可靠运行。

掌握阻焊层以获得高频成功

在复杂的高频 PCB 设计世界中,阻焊层厚度不仅仅是一个小细节,它是实现最佳信号完整性的关键因素。从影响阻抗到导致信号损失,阻焊层在射频电路的性能中起着关键作用。通过了解和控制射频电路的阻焊层厚度,考虑阻焊层介电常数,并解决阻焊层引起的信号损失,工程师可以释放其设计的全部潜力。

无论您是使用阻焊层微调阻抗控制,还是应对高频 PCB 设计的挑战,本指南中分享的见解和技巧都可以帮助您做出明智的决策。请记住,精度是射频设计中的一切,即使是最小的层(如阻焊层)也会产生很大的影响。与值得信赖的 PCB 制造服务合作,确保满足您的规格,并毫不犹豫地模拟和测试您的设计以获得最佳结果。

通过掌握阻焊层厚度的无名英雄,您离创建经得起时间考验的高性能、可靠的射频电路又近了一步。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号