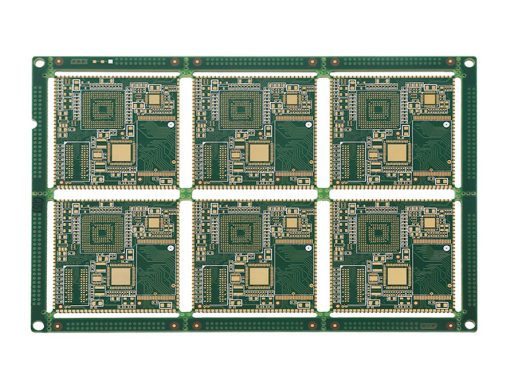

高速PCB叠层设计核心方法与实践指南

高速PCB叠层设计直接影响信号完整性、电磁兼容性和制造成本。本文从基础原则、结构规划、材料选择三方面,系统解析关键设计方法。

一、叠层设计基础原则

信号完整性优先

? 高速信号层需夹在电源或地平面之间,形成带状线结构。例如,第3层作为高速信号层时,上下需设置地平面。? 相邻信号层走线方向正交(如顶层X轴、次层Y轴),减少串扰。

电源与地平面布局

? 电源层与地层相邻,间距≤3mil,形成低阻抗耦合。例如,4层板常用结构:TOP-GND-PWR-BOTTOM。? 多电源层需分割区域,相邻信号层避免跨分割布线。

对称性与阻抗控制

? 采用偶数层结构(如4/6/8层),减少板材应力形变。例如,6层板推荐结构:TOP-GND-Signal-PWR-GND-BOTTOM。? 阻抗公差控制在±10%,使用FR4材料时介电常数(Er)选4.5-5.5。

二、常用叠层结构方案

4层板设计

? 方案一:TOP-Signal-GND-PWR-BOTTOM? 信号层与地平面相邻,适合中等密度设计。

? 方案二:TOP-PWR-GND-Signal-BOTTOM

? 电源层与地层隔离,适用于多电源系统。

6层板设计

? 方案一:TOP-GND-Signal1-PWR-GND-Signal2-BOTTOM? 高速信号层(Signal1)夹在双层地平面间,EMI抑制效果最佳。

? 方案二:TOP-Signal1-GND-PWR-Signal2-BOTTOM

? 两个信号层共用参考平面,需控制线宽匹配。

8层板设计

? 方案一:TOP-GND-Signal1-PWR-GND-Signal2-PWR-BOTTOM? 四层信号与四层参考平面,适合高复杂度BGA封装。

? 方案二:TOP-Signal1-GND-PWR-Signal2-GND-PWR-BOTTOM

? 电源层分割处理,需增加去耦电容密度。

三、关键设计参数控制

线宽与间距

? 1oz铜厚时,50Ω阻抗线宽:表层6mil/间距6mil,内层4mil/间距4mil。? 高频信号(>1GHz)线宽增加20%,补偿趋肤效应损耗。

过孔与盲埋孔

? 0.2mm间距BGA采用0.1mm激光盲孔,减少信号反射。? 背钻去除通孔残桩,残桩长度≤10mil。

材料选择

? 高速信号层使用Rogers 4350B(Er=3.66),损耗角正切(tanδ)≤0.004。? 电源层选用低损耗FR4(tanδ≤0.02),厚度0.2-0.5mm。

四、制造与验证要点

层压工艺

? 层压次数≤3次,避免层间滑移。温度控制在170-180℃,压力300-400psi。? 芯板与PP片厚度公差≤±10%,确保阻抗一致性。

测试验证

? T型探头法测量信号完整性,眼图张开度≥80%。? X射线检测盲孔填充率,铜覆盖≥95%。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号