PCB抗电磁干扰(EMI/EMC)设计技巧有哪些?

在电子设备日益小型化、高速化的趋势下,电磁兼容(EMC)设计已成为 PCB 设计的核心环节。电磁干扰(EMI)可能导致设备性能下降、通信中断甚至系统崩溃,尤其在医疗、航空航天等领域,EMC 不达标可能引发严重后果。本文将系统梳理 PCB 抗电磁干扰的设计技巧,从原理到实践,覆盖从源头抑制到测试验证的全流程。

1. EMC/EMI 基础原理介绍

电磁兼容(EMC)是指电子设备在电磁环境中正常工作,且不对其他设备产生无法忍受的电磁干扰的能力,包含两个核心维度:

电磁干扰(EMI):设备自身产生的电磁能量对其他设备造成的干扰,分为传导干扰(通过电源线、信号线传播)和辐射干扰(通过空间电磁波传播)。例如,开关电源的 MOS 管高频开关动作会产生 100MHz 以上的辐射干扰,可能影响周围收音机的正常接收。

电磁抗扰度(EMS):设备抵御外部电磁干扰的能力。例如,工业控制板需能在强电磁环境(如电机启动产生的脉冲干扰)中保持稳定运行。

EMI 的产生需满足三个条件:干扰源(如高频振荡器、开关电路)、耦合路径(如空间辐射、导线传导)、敏感设备(如高频接收器、模拟传感器)。PCB 设计的核心是通过优化布局布线,切断这三个要素的联系。

电磁干扰的频率特性差异显著:低频干扰(<30MHz)主要通过导线传导,高频干扰(>30MHz)则以辐射为主。例如,50Hz 工频干扰属于传导干扰,而 WiFi 模块的 2.4GHz 信号可能通过空间辐射干扰其他设备。

2. EMC 设计的三个基本路径:源、耦合路径、受体

针对 EMI 产生的三要素,EMC 设计需从以下三个路径同时入手:

抑制干扰源

降低开关速度:在满足时序要求的前提下,降低数字电路的边沿速率(如将 GPIO 的 slew rate 从 2ns 调整为 5ns),可减少高频谐波分量。测试表明,边沿速率降低 50%,100MHz 以上的辐射干扰可降低 15-20dB。

减小电流变化率(di/dt):在电源回路中增加缓冲电路(如 RC 吸收网络),抑制功率器件的瞬时电流尖峰。例如,在 DC-DC 转换器的续流二极管两端并联 100Ω 电阻 + 100pF 电容,可有效抑制反向恢复产生的干扰。

局部屏蔽干扰源:对高频振荡器、功率放大器等强干扰源,采用金属屏蔽罩(需良好接地)限制其电磁辐射范围。

切断耦合路径

抑制传导耦合:在电源线入口处安装 EMI 滤波器(如共模电感 + X/Y 电容),衰减传导干扰。例如,USB 接口处的共模电感可将传导干扰从 - 40dBμV 降至 - 60dBμV 以下。

阻断辐射耦合:增大干扰源与敏感电路的距离(至少 3 倍波长以上,对 1GHz 信号约 9cm),或在两者之间设置接地屏蔽板。

优化 PCB 布局:避免敏感信号线与干扰源线路平行布线,交叉时采用 90° 垂直交叉,减少互感耦合。

增强受体抗扰度

差分信号传输:将敏感模拟信号(如传感器输出)采用差分方式传输(如使用仪表放大器 AD8221),利用差分对的共模抑制能力(CMRR 通常 > 80dB)抵御外部干扰。

增加滤波电路:在敏感电路的输入端添加 RC 或 LC 滤波,例如在运算放大器的同相输入端串联 1kΩ 电阻 + 并联 100pF 电容到地,可滤除高频干扰。

强化接地设计:敏感电路采用独立接地回路,避免与干扰源共享接地路径,降低地电位差带来的干扰。

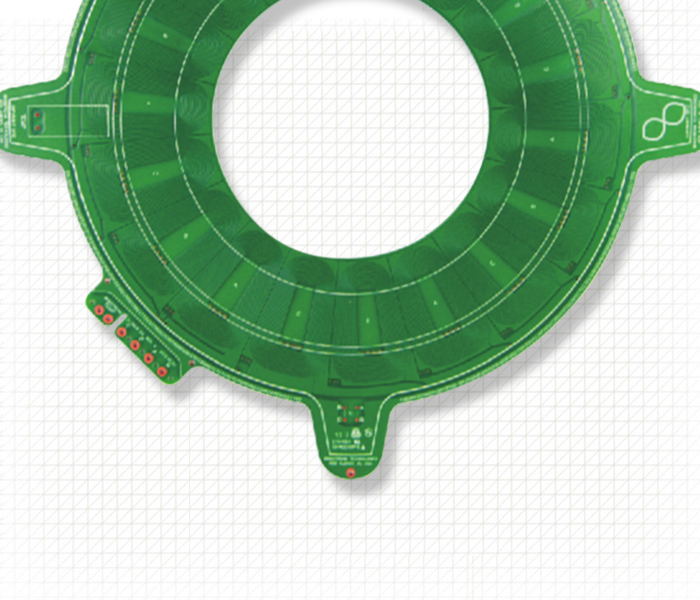

3. 地平面完整性与层叠结构优化

地平面是 EMC 设计的 “基石”,其完整性直接影响干扰的传播与抑制:

地平面设计原则

保持地平面连续:避免在地平面上开槽或分割(除非必须区分模拟地与数字地),完整的地平面可提供低阻抗回流路径,减少辐射。例如,某 4 层板设计中,地平面开槽导致 100MHz 辐射干扰增加 25dB,恢复完整性后干扰降至合格范围。

单点接地分区:数模混合电路中,模拟地(AGND)与数字地(DGND)需在电源入口处单点连接(如通过 0Ω 电阻或磁珠),避免形成地环路。连接点应远离敏感模拟电路(如 ADC 的参考地)。

高频信号回流路径最短:高速信号线(如 DDR3 的 CLK)下方必须有完整的地平面,且走线长度与回流路径长度之差控制在信号波长的 1/20 以内(1GHz 信号约 1.5cm),减少辐射面积。

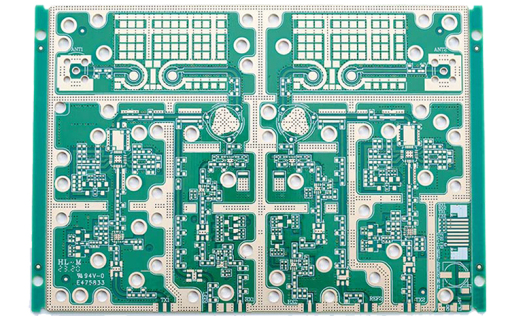

层叠结构优化

高速信号层紧邻地平面:如 6 层板推荐叠层(从上到下):顶层信号(高速)→ GND → 电源 → 中间信号 → GND → 底层信号,确保高速信号的回流路径仅在相邻地平面内。

电源层与地平面紧邻:利用电源层与地平面之间的寄生电容(通常每 cm2 约 1pF)作为分布式去耦电容,增强电源稳定性。层间距控制在 0.1-0.2mm(如 4 层板的电源层与地平面间距 0.15mm),可获得更好的滤波效果。

厚铜地层增强屏蔽:对强干扰环境(如工业电机附近),地层采用 2oz 铜厚(70μm),利用趋肤效应增强高频屏蔽能力,比 1oz 铜厚的屏蔽效果提升约 5dB。

4. 高频信号走线规则与终端匹配

高频信号(>100MHz)的走线是辐射干扰的主要来源,需遵循以下规则:

基本走线原则

短而直:高频信号线长度应≤λ/10(λ 为信号波长),例如 1GHz 信号的走线长度应≤3cm。必须长距离传输时,采用差分线或屏蔽线。

线宽与间距:微带线特性阻抗控制在 50±10%(高速数字信号)或 75±10%(射频信号),线宽根据叠层计算(如 4 层板中 50Ω 微带线在 FR-4 基材上约 0.25mm 宽)。线间间距≥3 倍线宽,减少串扰。

避免直角与 Stub:走线拐角采用 45° 或圆弧过渡(半径≥3 倍线宽),消除直角带来的阻抗不连续;禁止出现无驱动的 Stub 线(长度应 <λ/20),否则会产生反射干扰。

差分信号设计

等长等距:差分对的两根线长度差需 < 5mil(127μm),间距保持一致(通常 0.1-0.2mm),确保差分阻抗稳定(如 90±10%Ω)。例如,USB 3.0 的差分对长度差要求 < 3mil。

对称布线:差分线需平行走线,避免交叉或分支,必要时通过 “蛇形线” 补偿长度,但蛇形线的节距应 > 5 倍线宽,减少额外损耗。

包地处理:对高速差分线(如 PCIe、HDMI)采用单边或双边包地(接地屏蔽线),包地需多点接地(间隔 <λ/20),但需注意包地与差分线的间距≥2 倍线宽,避免影响阻抗。

终端匹配技巧

串联匹配:在信号源端串联电阻(R = Z0 - Zs,Zs 为源阻抗),适用于源端阻抗低于传输线阻抗的场景。例如,50Ω 传输线配 33Ω 源阻抗时,串联 17Ω 电阻可消除反射。

并联匹配:在接收端并联电阻(R = Z0)到地或电源,适用于高频信号(>1GHz),但会增加功耗。

AC 匹配:采用 RC 并联网络(如 100Ω + 100pF),在高频段提供匹配,低频段不影响信号电平,适用于时钟信号等。

5. 电源滤波与去耦措施

电源系统是 EMI 在 PCB 内部传播的主要路径,良好的滤波与去耦设计可大幅降低电源噪声:

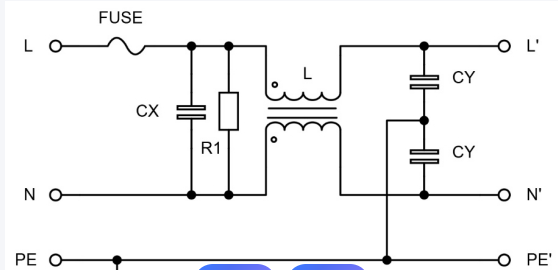

电源入口滤波

多级滤波:在系统电源入口处采用 “π 型” 滤波器(C-L-C 结构),如 220nF X 电容 + 共模电感(10mH) + 100nF Y 电容,可同时抑制差模与共模干扰。

隔离变压器:对敏感电路(如医疗设备),采用带屏蔽层的隔离变压器(隔离电压≥2kV),阻断共模干扰传导路径。

去耦电容网络

多层电容组合:在 IC 电源引脚旁按 “小容量 + 大容量” 组合放置去耦电容,如 0.1μF(100MHz 谐振)+ 10μF(10MHz 谐振)+ 100μF(1MHz 谐振),覆盖 10kHz-1GHz 的噪声频段。

放置原则:0.1μF 电容距离引脚 < 5mm,10μF 电容 < 15mm,确保高频噪声的回流路径最短。BGA 封装芯片需在底部焊盘区域均匀布置 0402 封装的 0.1μF 电容,每 4 个电源引脚至少 1 颗。

接地优化:去耦电容的接地过孔应紧邻电容焊盘(距离 < 2mm),并直接连接到地平面,避免长走线引入寄生电感。

线性稳压器与 DC-DC 处理

LDO 外围滤波:在 LDO 的输入端(10μF 电解电容)和输出端(1μF 陶瓷电容)加强滤波,抑制输入纹波和输出噪声。例如,低压差 LDO(如 AMS1117)输出端的 1μF 电容可将噪声从 50μVrms 降至 10μVrms。

DC-DC 屏蔽:将 DC-DC 转换器及其电感、续流二极管放置在 PCB 边缘,周围设置接地隔离带,避免其开关噪声耦合到敏感电路。

6. EMI 抑制常用器件:磁珠、电感、TVS 等

合理选用 EMI 抑制器件是快速解决 EMC 问题的关键:

磁珠(Ferrite Bead)

特性:在高频段呈现高阻抗(如 100MHz 时阻抗 500Ω),对直流电阻小(<1Ω),适用于抑制信号线或电源线的高频噪声。

选型:根据干扰频率选择磁珠的阻抗曲线,确保在目标频率点阻抗 > 100Ω。例如,抑制 2.4GHz WiFi 干扰,可选用在该频率阻抗 > 600Ω 的磁珠(如 BLM18PG601SN1)。

应用:串联在敏感信号线(如 I2C、SPI)或低速接口(如 UART)上,或并联在电源与地之间作为吸收元件。

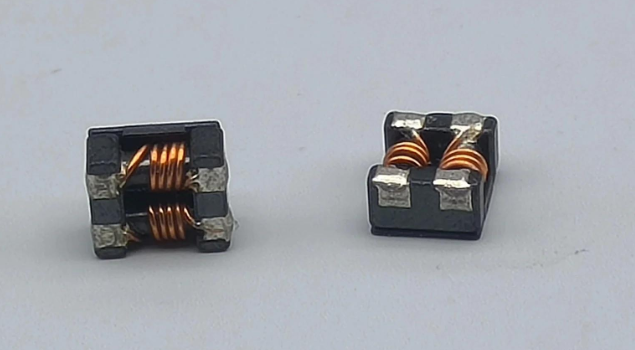

共模电感(Common Mode Choke)

特性:对共模信号呈现高阻抗,差模信号呈现低阻抗,主要用于抑制电源线或信号线的共模干扰。

选型:根据额定电流(≥1.5 倍工作电流)和阻抗(100MHz 时≥1000Ω)选择,例如 USB 2.0 接口选用额定电流 500mA、100MHz 阻抗 1500Ω 的共模电感。

应用:安装在设备电源线入口或高速接口(如 HDMI、Ethernet)的差分线上,靠近连接器端放置。

TVS 二极管(Transient Voltage Suppressor)

特性:能快速(ns 级)吸收瞬态高压脉冲(如 ESD、浪涌),保护电路免受冲击。

选型:反向击穿电压(VRWM)应高于工作电压(如 3.3V 电路选 VRWM=5V),峰值脉冲电流(IPP)根据防护等级选择(如接触放电 8kV 需 IPP≥20A)。

应用:并联在接口信号线上(如 USB 的 D+、D-),靠近连接器放置,走线长度 < 5mm,确保瞬态能量优先通过 TVS 释放。

穿心电容(Feedthrough Capacitor)

特性:通过金属外壳与屏蔽体直接连接,消除了传统电容的引脚电感,高频滤波效果优异(可达 1GHz 以上)。

应用:用于穿透金属屏蔽罩的信号线或电源线,如在射频模块的屏蔽罩上安装穿心电容,抑制屏蔽体内外的电磁耦合。

7. 外围接口(如 USB)走线屏蔽处理

外围接口是 EMI 进出设备的主要 “窗口”,需重点处理:

USB 接口设计

差分线处理:USB 2.0 的 D+、D - 差分对需严格等长(误差 < 5mil),阻抗控制在 90Ω±10%,走线长度 < 50cm(USB 3.0<30cm)。

屏蔽层接地:USB 线缆的屏蔽层需单端接地(通常在主机端通过 330Ω 电阻接地),避免形成地环路。PCB 上的 USB 接口屏蔽壳需通过多点接地(至少 2 个接地过孔)连接到地平面。

ESD 防护:在 D+、D - 线靠近连接器处并联 TVS 二极管(如 SMF05C),并在 VBUS 线上串联自恢复保险丝(如 100mA)+ TVS(如 SMBJ5.0A),抵御静电和过压冲击。

HDMI 接口设计

屏蔽与隔离:HDMI 接口的 19 对差分线需整体包裹在接地屏蔽层内,屏蔽层与接口金属壳可靠连接。PCB 上的 HDMI 信号区域需与其他电路保持 5mm 以上距离,周围设置接地隔离带。

阻抗匹配:TMDS 差分对阻抗控制在 100Ω±10%,每对差分线长度差 < 10mil,总长度 < 1m。

电源滤波:HDMI 的 5V 电源输入端需串联磁珠 + 并联 100nF 电容,抑制电源噪声耦合到信号线上。

网口(Ethernet)设计

隔离变压器:网口必须通过隔离变压器(如 HR911105A)与 PHY 芯片连接,实现电气隔离,抑制共模干扰。变压器中心抽头需通过 100nF 电容接地。

磁珠与 TVS:在差分对(TX±、RX±)上串联共模电感,并联 TVS 二极管(如 PESD5V0U2BT),增强抗扰度。

PCB 布局:网口变压器和连接器需放置在 PCB 边缘,与 PHY 芯片的距离 < 10cm,避免长距离走线引入干扰。

8. 整体设计流程中的 EMC 测试与验证方法

EMC 设计需结合测试验证,形成 “设计 - 测试 - 优化” 的闭环:

前期仿真与预测试

SI/PI 仿真:在布线阶段使用仿真工具(如 Allegro SI、Cadence Clarity)分析高速信号的反射、串扰和电源噪声,提前优化设计。例如,通过仿真发现 DDR3 的地址线串扰超标,可增加线间距从 0.2mm 至 0.3mm。

近场扫描:使用近场探头(如 H 场探头、E 场探头)在 PCB 调试阶段扫描高频区域,定位强辐射点(如时钟振荡器、未端接的信号线),早期发现问题。

正式 EMC 测试项目

辐射发射(RE)测试:在 3 米法或 10 米法暗室中,测试设备在 30MHz-18GHz 频段的辐射干扰,需满足标准限值(如 CISPR 32 Class B 要求 30-1000MHz≤54dBμV/m)。

传导发射(CE)测试:通过 LISN(线路阻抗稳定网络)测试电源线在 150kHz-30MHz 的传导干扰,限值通常为 40-60dBμV。

静电放电(ESD)测试:按照 IEC 61000-4-2 标准,对设备进行接触放电(±4kV、±8kV)和空气放电(±8kV、±15kV)测试,观察设备是否正常工作。

快速脉冲群(EFT)测试:在电源线和信号线上施加 1kV-4kV 的快速脉冲群,验证设备的抗扰能力。

测试问题定位与解决

辐射超标的定位:通过近场探头结合频谱分析仪,确定辐射源位置(如未屏蔽的晶振、过长的 GPIO 线),针对性采取屏蔽、滤波或改线措施。

传导超标的解决:若某一频率点传导超标,可在电源入口处增加该频率的陷波滤波器(如串联 LC 谐振电路),或更换更高抑制能力的 EMI 滤波器。

抗扰度失败的优化:对敏感信号增加滤波(如 RC 网络)、强化接地(如缩短接地路径)或采用差分传输,提升抗扰度。

EMC 设计是一门 “预防为主” 的工程学科,80% 的 EMC 问题可通过前期布局布线优化解决。核心原则是:保持地平面完整、控制高速信号阻抗、合理设置滤波与屏蔽、强化接口防护。在实际设计中,需结合电路特性(如频率、功率)和应用场景(如工业、医疗)灵活调整方案,并通过测试验证不断优化,才能最终实现产品的 EMC 合规。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号