阻抗控制PCB的经济高效的叠层策略

设计阻抗控制印刷电路板 (PCB) 不必花太多钱。通过专注于智能层数决策、战略材料选择和优化叠层设计,您可以在不牺牲性能的情况下显着降低 PCB 制造成本。

为什么阻抗控制在 PCB 设计中很重要

在探索成本节约策略之前,让我们先了解一下为什么阻抗控制至关重要。在高速数字电路中,例如电信、计算和射频应用中使用的电路,保持一致的阻抗对于信号完整性至关重要。如果走线的阻抗与源或负载不匹配,则可能导致信号反射、串扰和数据丢失。例如,典型的高速设计可能将单端走线的特性阻抗设置为 50 欧姆,差分对的特性阻抗为 100 欧姆,以确保正确的信号传输。

然而,由于更严格的公差、专用材料和复杂的叠层,实现这种精度通常会带来更高的 PCB 制造成本。好消息是,通过正确的方法,您可以在不影响质量的情况下实施廉价的阻抗控制。让我们探讨如何通过具有成本效益的叠加策略来做到这一点。

策略 1:优化层数以降低成本

降低 PCB 制造成本最有效的方法之一是仔细选择层数。每增加一层就会增加制造复杂性、材料使用和测试要求,从而推高成本。以下是解决这个问题的方法:

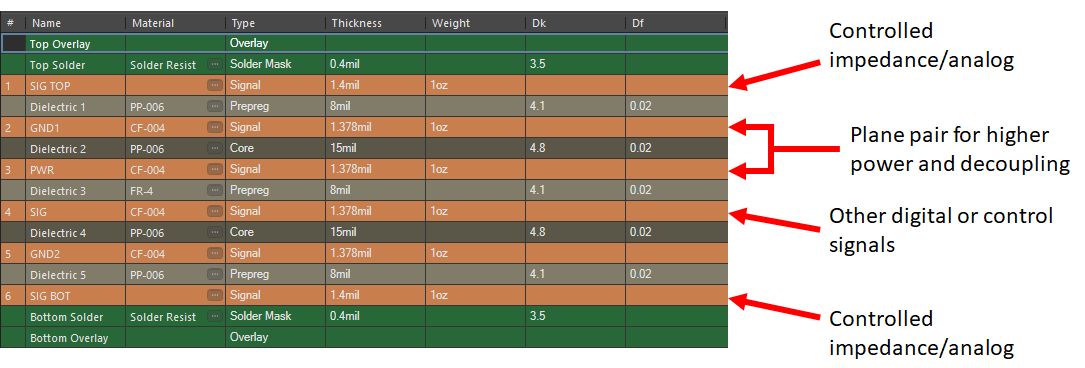

最小化图层:对于许多高速设计,4 层或 6 层 PCB 就足够了,而不是跳到 8 层或更多层。例如,如果设计得当,具有两个信号层和两个接地层的 4 层板通常可以为高达 5 GHz 的信号提供足够的阻抗控制。

有效使用接地层:将接地层放置在信号层附近,以创建稳定的阻抗参考。这减少了仅用于参考平面的额外层的需求,从而降低了成本。

评估设计需求:评估您的设计是否真的需要多层。如果您的电路工作频率低于 1 GHz,则层数更少的更简单叠层仍可能满足阻抗目标,而无需额外费用。

通过减少层数,您可以在保持性能的同时显着降低 PCB 成本。但是,请始终模拟您的设计,以确保更少的层不会影响信号完整性。

策略二:智能选材实现廉价阻抗控制

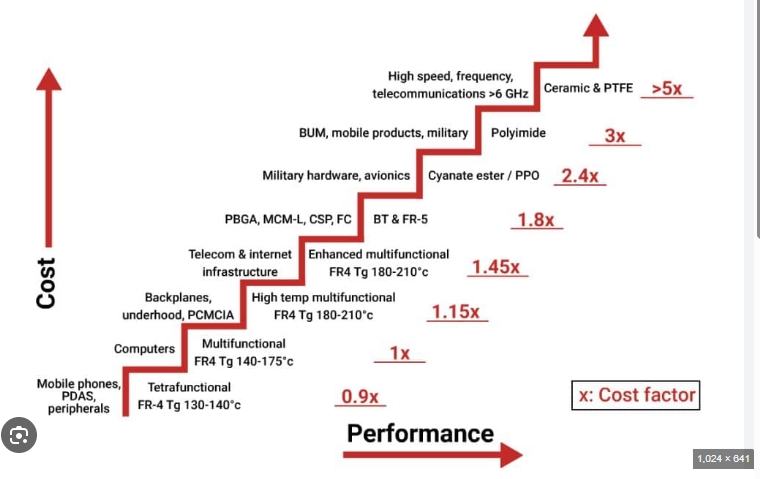

材料的选择在阻抗控制和 PCB 制造成本中都起着巨大的作用。Rogers 或 Isola 等高性能材料因其稳定的介电常数 (Dk) 和低损耗正切 (Df) 而经常用于严格的阻抗要求。然而,这些材料可能很昂贵。以下是如何选择材料以节省成本:

用于低频的标准 FR-4:对于工作频率低于 2 GHz 的设计,Dk 约为 4.2-4.6 的标准 FR-4 材料通常可以满足阻抗需求,而成本仅为优质层压板的一小部分。这是许多消费电子和工业应用的理想选择。

混合叠层:如果高频信号仅限于特定层,请考虑混合方法。对电源层和接地层使用具有成本效益的 FR-4,仅为关键信号层保留更高等级的材料。与完整的高端材料叠层相比,这可以降低高达 30% 的成本。

与制造商合作:与您的 PCB 制造商合作,确定具有相似电气性能但成本较低的替代材料。许多制造商提供平衡性能和经济性的内部材料选择。

通过在材料选择方面做出明智的决策,您可以在不牺牲高速信号可靠性的情况下实现廉价的阻抗控制。

策略 3:设计阻抗和成本效益叠层

叠层设计直接影响阻抗控制和制造复杂性。精心规划的叠层可以帮助您避免代价高昂的过度设计,同时满足性能目标。考虑以下提示:

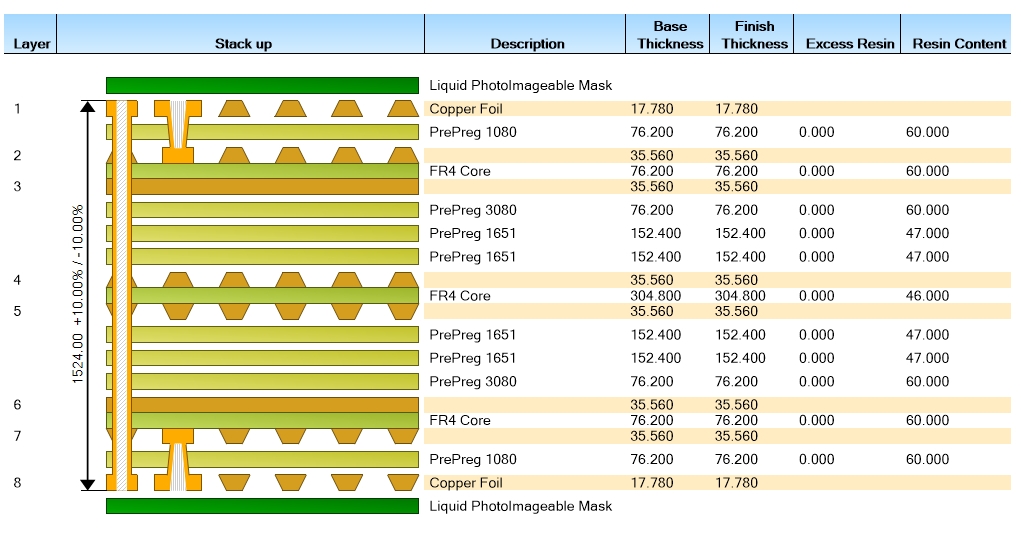

对称叠层:设计对称的叠层以防止制造过程中翘曲,这可能导致阻抗不一致和代价高昂的返工。例如,在 6 层板中,确保磁芯两侧的电介质厚度和铜重量平衡。

控制介电厚度:阻抗在很大程度上受信号走线与其参考平面之间的距离影响。使用更薄的电介质(例如 4-5 密耳)来进行更严格的阻抗控制,但避免低于制造商的最低值,以防止增加成本。FR-4 上 50 欧姆走线的常见目标是介电厚度约为 6 密耳,走线宽度为 5-7 密耳。

尽可能使用更宽的迹线:在阻抗一致的情况下,制造更宽的走线更容易、更便宜。窄迹线需要更严格的公差,从而增加成本。如果空间允许,请选择更宽的走线(例如,6-8 密耳而不是 3-4 密耳)以达到阻抗目标。

这些叠层策略有助于保持信号完整性,同时有助于降低 PCB 成本。在完成设计之前,请务必使用仿真工具来验证阻抗值。

策略 4:利用设计工具实现精度和节省成本

现代 PCB 设计软件包括根据叠层、材料和走线几何形状计算和仿真阻抗的功能。使用这些工具可以避免昂贵的设计迭代并确保廉价的阻抗控制。以下是如何充分利用它们:

阻抗计算器:许多设计平台提供内置计算器,可根据走线宽度、间距和介电特性预测阻抗。例如,在具有 6 密耳电介质的标准 FR-4 板上,50 欧姆走线可能需要 5.5 密耳的走线宽度和 8 密耳的差分对间距。

模拟:在制造前运行信号完整性仿真以识别反射或串扰等潜在问题。这可以通过避免重新设计来节省大量成本。

尽早协作:在设计阶段与制造商分享您的叠层和阻抗要求。他们可以提供有关公差的反馈并提出调整建议以降低 PCB 制造成本。

预先投入时间进行设计优化可以减少错误并确保您的电路板在第一次尝试时就达到阻抗目标,从而节省大量成本。

策略 5:简化制造流程以降低成本

制造过程本身就提供了降低 PCB 成本的机会。阻抗控制板通常需要额外的测试和更严格的过程控制,这会增加成本。以下是简化生产的方法:

标准公差:除非您的设计绝对需要超严格的阻抗容差(例如,±5%),否则请选择 ±10% 的标准容差。这减少了对广泛测试的需求并降低了成本,而不会显着影响大多数应用程序的性能。

面板化效率:设计您的 PCB,以在制造过程中最大限度地利用面板。高效的布局减少了材料浪费并降低了 PCB 制造成本。

尽量减少特殊流程:避免不必要的微孔或埋孔,除非对您的设计至关重要。这些功能增加了复杂性和成本。坚持使用通孔过孔,实现更简单、更便宜的制造。

通过关注可制造性,您可以实现廉价的阻抗控制,同时控制生产费用。

平衡成本和性能:关键要点

通过正确的策略,在预算内设计阻抗控制的 PCB 是完全可能的。回顾一下,重点关注 PCB 成本降低和廉价阻抗控制的这些核心原则:

通过最大限度地减少不必要的层并有效使用接地层来优化层数。

在材料选择时做出明智的选择,将 FR-4 等经济高效的选项用于非关键层或低频设计。

设计具有受控介电厚度和更宽走线的对称叠层,以平衡阻抗和成本。

使用设计工具进行仿真和验证阻抗,降低昂贵的返工风险。

通过遵守标准公差和高效的面板设计来简化制造。

通过应用这些经济高效的叠层策略,您可以保持高速应用的信号完整性,同时控制 PCB 制造成本。无论您是在制作小型原型还是大型生产,这些技巧都可以帮助您在不超支的情况下实现可靠的性能。

阻抗控制 PCB 是现代电子产品的基石,可确保高速信号传输时不会失真或丢失。虽然实现精确的阻抗控制似乎成本高昂,但在层数、材料选择和叠层设计方面的战略决策可以显着降低 PCB 成本。通过遵循本指南中概述的方法,您可以实施满足您的技术要求并符合您预算的廉价阻抗控制。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号