解码最小走线间距:PCB设计人员综合指南

了解最小走线间距对于旨在确保设计功能性、安全性和可靠性的 PCB 设计人员至关重要。无论您关心高压安全、信号完整性还是遵守行业标准,正确的走线间距都可以决定您的项目的成败。在本指南中,我们将详细介绍高压最小走线间距、信号完整性最小走线间距、最小走线间距 IPC 2221 指南以及如何使用最小走线间距计算器来简化设计流程的要点。让我们深入了解细节,以帮助您创建强大且高效的 PCB 布局。

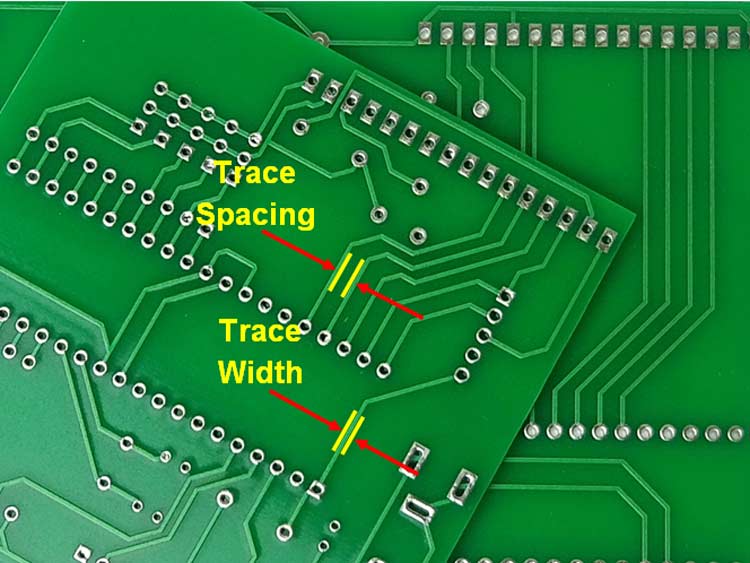

PCB 设计中的最小走线间距是多少?

最小走线间距是指印刷电路板 (PCB) 上两条导电走线之间允许的最小距离。该间距对于防止信号之间的短路、电弧或干扰等电气问题至关重要。它直接影响 PCB 的安全性和性能,特别是在涉及高压或高速信号的应用中。电压水平、环境条件和传输的信号类型等因素都会影响所需的间距。

在以下部分中,我们将探讨走线间距如何应用于不同的设计场景,并提供实现最佳结果的实用见解。无论您是初学者还是经验丰富的设计师,本指南都将为您提供有效应对走线间距挑战的知识。

为什么最小走线间距在 PCB 设计中很重要

走线间距不仅仅是一个随机设计规则,它是确保 PCB 按预期运行的基本方面。间距不当可能会导致灾难性故障,包括电气短路、信号衰减,甚至高压应用中由于电弧而导致的电路板损坏。通过保持正确的间距,您可以保护您的设计免受这些风险并确保符合行业标准。

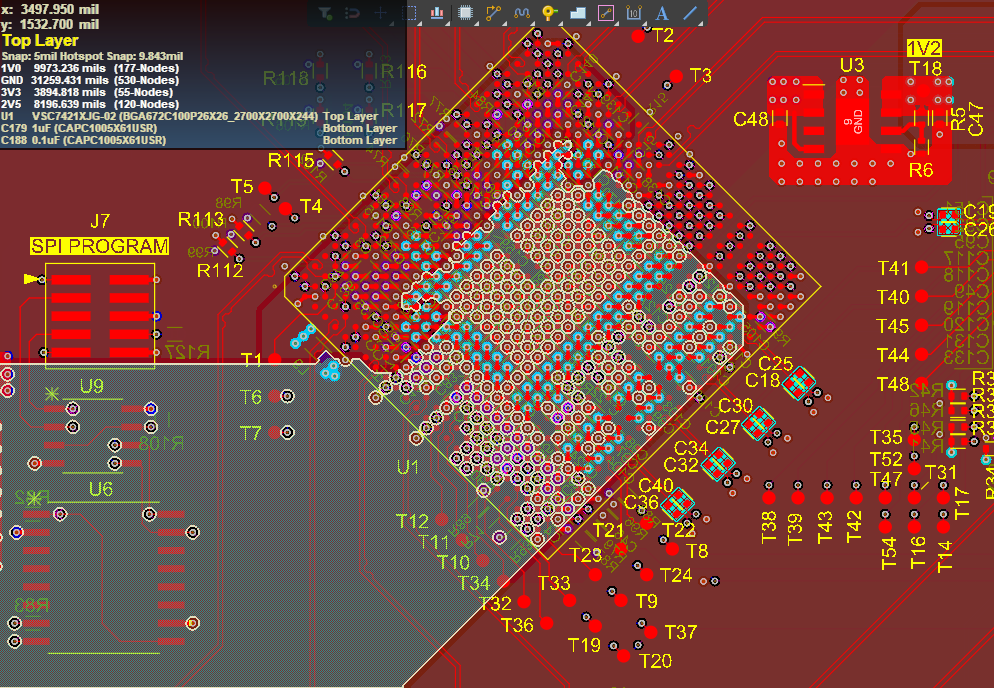

除了安全之外,走线间距还会影响制造成本和电路板尺寸。更紧的间距可以减少 PCB 的整体占地面积,但它通常需要更精确的制造技术,这会增加成本。平衡这些因素是成功设计的关键。

适用于高压应用的最小走线间距

在处理PCB设计中的高压时,安全成为重中之重。高压的最小走线间距确保导电元件之间有足够的距离,以防止绝缘材料产生电弧或击穿。电压越高,需要的间距越大,以避免放电。

例如,在 500V 下运行的设计中,可能需要至少 2.5 毫米的间距,具体取决于 PCB 材料的介电强度以及湿度或海拔等环境因素。对于千伏范围内的电压,这些值可能会显着增加。高压设计通常需要额外的考虑,例如使用更宽的走线或特殊涂层来增强绝缘性。

这里的一个关键概念是爬电距离和间隙。爬电距离是指两个导电部件沿绝缘材料表面的最短路径,而间隙是穿过空气的最短距离。在高压设计中必须考虑到这两者,以防止意外电流流动。行业标准根据电压水平和应用类型为这些距离提供了具体指南,我们将在稍后的 IPC 2221 中讨论。

最小走线间距,确保信号完整性

在高速数字电路或敏感模拟设计中,信号完整性的最小走线间距在保持性能方面起着关键作用。当走线太近时,它们可能会出现串扰,其中来自一条走线的信号会干扰另一条走线,从而导致数据错误或噪声。适当的间距有助于最大限度地减少电磁干扰 (EMI) 并确保干净的信号传输。

例如,在高速信号工作频率为 1 GHz 的设计中,可能需要 3 倍走线宽度的间距来减少串扰。该经验法则根据信号频率、电路板材料的介电常数和走线几何形状而变化。此外,阻抗匹配在此类设计中变得至关重要。受控阻抗走线通常需要与相邻走线或接地层保持特定的间距,以保持一致的特性阻抗,例如许多射频应用的 50 欧姆。

为了实现最佳的信号完整性,设计人员还必须考虑接地层的布局和差分对的使用,其中承载互补信号的走线布线靠得很近,但与外部走线的间距受控。这些技术有助于降低噪声并提高信号质量。

了解 IPC 2221 标准的最小走线间距

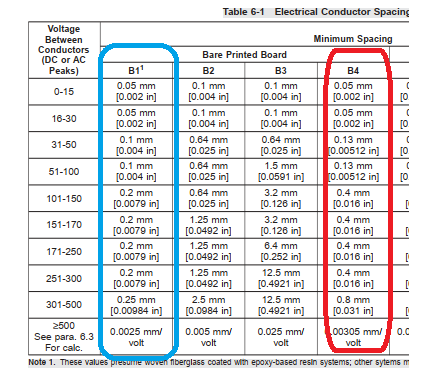

最小走线间距 IPC 2221 标准是广泛认可的 PCB 设计指南,根据电压、环境条件和应用类型提供了走线间距的详细要求。IPC 2221 标题为“印制板设计通用标准”,概述了安全间距,以确保可靠性并防止电气故障。

根据 IPC 2221,走线间距要求根据走线是在外层还是内层以及是涂层还是未涂层进行分类。例如,对于无涂层外层的电压为 100V,建议最小间隙为 0.6mm。该值随着电压升高或环境条件(例如高湿度或污染水平)而增加,这会降低空气或板材的绝缘性能。

该标准还提供了计算爬电距离和电气间隙的表格和公式,并考虑了 PCB 的污染程度和材料组。从事高压或安全关键型应用的设计人员必须遵守这些准则,以确保合规性并避免代价高昂的重新设计或故障。

使用最小走线间距计算器实现高效设计

手动计算每种场景的走线间距可能非常耗时且容易出错,尤其是在处理复杂设计时。这就是最小走线间距计算器变得无价的地方。这些工具允许设计人员输入电压、层类型和环境条件等参数,以立即获得推荐的间距值,从而简化了流程。

许多在线计算器都基于 IPC 2221 等行业标准,确保结果符合公认的准则。例如,通过输入 300V 的电压并指定外部未涂层层,计算器可能会输出 1.5 毫米的最小间隙。一些高级工具还考虑了信号完整性因素,为高速设计提供间距建议,以最大限度地减少串扰和 EMI。

使用计算器不仅可以节省时间,还可以降低人为错误的风险,确保您的设计满足安全和性能要求。这些工具在布局规划的早期阶段特别有用,使您能够快速迭代和优化设计。

影响最小走线间距的因素

有几个因素决定了给定 PCB 设计的适当走线间距。了解这些可以帮助您做出明智的决策并创建平衡性能、安全性和可制造性的布局。

电压水平:更高的电压需要更大的间距以防止电弧或介电击穿。例如,在 1kV 下运行的设计可能需要 8mm 或更大的间隙,具体取决于标准和条件。

信号频率:高频信号更容易受到串扰和 EMI 的影响,因此需要更宽的间距或特定的布线策略(例如差分对)。

环境条件:湿度、温度和污染等因素会影响空气和 PCB 材料的绝缘性能,在恶劣环境中需要更大的间距。

板材:PCB 基板的介电强度和性能会影响其可以承受的电压,从而影响间距要求。

制造限制:由于需要精密制造,更紧的间距会增加生产成本。请务必咨询您的制造商,了解他们的能力和公差。

通过在设计阶段考虑这些因素,您可以避免常见陷阱并确保您的 PCB 在其预期应用中可靠地运行。

实现最小迹线间距的实用技巧

现在我们已经介绍了走线间距背后的理论,让我们看看一些可行的技巧,以在您的设计中应用这些原则。

使用带有内置规则的设计软件:现代 PCB 设计工具允许您根据电压或信号类型设置间距约束,并在布局过程中自动标记违规行为。

尽早规划爬电距离和间隙:确定原理图中的高压区域,并在初始布局期间分配足够的空间,以避免设计局促。

咨询行业标准:始终参考 IPC 2221 等指南了解间距要求,特别是对于安全关键型或高压应用。

测试和验证:完成布局后,执行设计规则检查 (DRC),并在可能的情况下进行原型测试,以验证间距是否满足性能和安全需求。

与制造商合作:与您的 PCB 制造商密切合作,确保您的间距设计符合他们的制造能力和公差。

遵循这些步骤可以帮助简化您的设计流程并减少代价高昂的修订或失败的可能性。

走线间距要避免的常见错误

即使是经验丰富的设计师在走线间距方面也会犯错误。以下是一些需要注意的常见陷阱:

忽视环境因素:未能考虑湿度或温度变化可能会导致间距不足并导致现场出现潜在故障。

忽视内部层:内层和外层的间距规则不同。由于更好的绝缘性,内层通常需要较小的间距,但这仍然必须准确计算。

忽视信号完整性需求:仅关注电压间隔而忽略串扰或阻抗问题可能会降低高速设计的性能。

假设间距均匀:并非 PCB 上的所有走线都有相同的间距要求。与低功耗走线相比,高压和高速走线可能需要独特的考虑。

通过保持警惕并根据标准和要求仔细检查您的设计,您可以避免这些错误并创建更可靠的 PCB。

掌握最小走线间距以实现更好的 PCB 设计

最小走线间距是有效 PCB 设计的基石,影响着从高压应用的安全性到高速电路性能的方方面面。通过了解高压最小走线间距、信号完整性最小走线间距背后的原理,并遵守最小走线间距 IPC 2221 等标准,您可以创建既安全又高效的设计。此外,利用最小迹线间距计算器等工具可以节省时间并提高工作流程的准确性。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号