PCB布线长度过长会导致哪些问题,该如何控制?

在 PCB 设计中,布线长度是影响信号完整性和电路性能的关键因素之一。尤其在高速、高频电路中,看似微小的长度差异可能引发严重的功能故障。合理控制布线长度,是确保电路稳定运行的基础设计原则。

线路过长带来的信号延迟与串扰问题

布线长度过长是 PCB 设计中常见的隐性问题,其危害随信号频率升高而显著加剧。对于低速电路(如≤1MHz),短线与长线的差异可能难以察觉;但在高速电路(如≥100MHz)中,过长的布线会导致信号延迟超出时序容忍范围,引发数据传输错误。同时,长线形成的 “天线效应” 会增强电磁辐射,加剧与相邻线路的串扰(Crosstalk),导致信号信噪比下降。

例如,在 1GHz 高速数字电路中,10cm 的布线延迟约为 0.5ns,若超过芯片时序要求的 0.3ns,会直接导致数据采样错误;而长线与相邻线路的耦合电容增加,可能使串扰电压超过信号摆幅的 10%,破坏信号完整性。因此,控制布线长度是高速 PCB 设计的核心任务之一。

原理解析:传播延迟、信号反射与回路面积影响

布线长度过长的危害源于三个核心物理效应:

传播延迟增大

信号在 PCB 布线中的传播速度由介质特性决定,公式为:

传播速度(cm/ns)= 30 / √εr

(其中 εr 为介质介电常数,FR-4 的 εr≈4.4,故传播速度≈15cm/ns,即每厘米延迟约 0.067ns)。

布线越长,总延迟越大。当延迟超过信号周期的 1/10(高速电路典型阈值),信号会呈现 “传输线效应”,接收端无法正确识别信号状态。例如,100MHz 信号周期为 10ns,若布线延迟超过 1ns(约 15cm),需按传输线规则设计,否则会因延迟导致时序紊乱。

信号反射加剧

长线布线中,任何阻抗不连续(如线宽变化、过孔、拐角)都会引发信号反射。反射信号与原信号叠加,会导致信号波形失真(如过冲、振荡)。布线越长,反射次数越多,失真越严重。例如,50cm 长的信号线可能经历多次反射,使信号上升沿从 1ns 拉长至 3ns,超出芯片输入容限。

回路面积扩大

信号回流路径随布线长度增加而延长,形成的 “信号 - 回流” 回路面积增大。根据电磁学原理,回路面积越大,对外辐射的电磁干扰(EMI)越强,同时抗外部干扰能力越弱。例如,30cm 长的布线形成的回路面积可能是 10cm 布线的 9 倍,EMI 辐射强度显著提升,可能导致产品无法通过电磁兼容测试。

控制策略:短线原则、紧靠焊盘走线、关键线最小化

控制布线长度需从设计策略入手,结合布局与布线技巧:

短线原则:优先规划最短路径

布局优化:将功能相关的元器件就近摆放(如芯片与外围电阻、电容距离≤5cm),减少布线长度。例如,时钟芯片应靠近被驱动的芯片,避免时钟线跨板布线。

避免绕线:布线时走 “直线优先”,必要时通过 “打孔换层” 缩短路径,而非在同一层迂回绕线。高速信号(如 PCIe、USB)需严格禁止无意义绕线。

紧靠焊盘走线:减少冗余长度

布线从焊盘引出后直接走向目标点,避免 “从焊盘引出后先拐向无关方向再回头” 的冗余路径。例如,贴片电阻的两端布线应从焊盘边缘直接延伸,长度控制在 2-3mm 内。

多引脚芯片(如 QFP、BGA)的引脚布线应 “扇出后直接布线”,扇出长度≤2mm,避免在引脚区域形成 “蛛网式” 绕线。

关键线最小化:区分信号优先级

最高优先级:时钟线、高速差分对(如 DDR 数据总线)、复位信号线,长度需控制在最短(如时钟线≤10cm,具体按芯片手册要求)。

次高优先级:控制总线(如 I2C、SPI),长度建议≤20cm。

普通优先级:低速信号线(如 GPIO),长度可放宽至 30-50cm,但需避免与高速线平行。

软件设置建议:DRC 规则配置及告警设置

利用 PCB 设计软件的 DRC 功能,可自动监控布线长度,及时预警过长线路:

Altium Designer 设置步骤:

新建线长规则:

点击 “Design”→“Rules”→“High Speed”→“Maximum Length”;

点击 “New Rule”,命名为 “Clock_Max_Length”,在 “Where The Object Matches” 中选择 “Net Class=Clock”(时钟网络类);

在 “Value” 栏设置最大长度(如 1000mil=25.4mm)。

批量设置不同网络:

为高速信号(如 “DDR_Data”)创建单独规则,设置长度限制(如 1500mil);

为普通信号设置通用规则(如 5000mil)。

启用实时告警:

勾选 “Tools”→“Design Rule Check” 中的 “Maximum Length”;

布线时,若长度超过限制,软件会实时以红色高亮显示,并在 “Messages” 面板提示告警。

KiCad 设置步骤:

打开 “PCB Editor”→“File”→“Board Setup”→“Design Rules”→“Constraints”;

在 “Net Classes” 中为不同网络类设置 “Max Length”;

点击 “Run DRC”,过长线路会在报告中标记,点击即可定位。

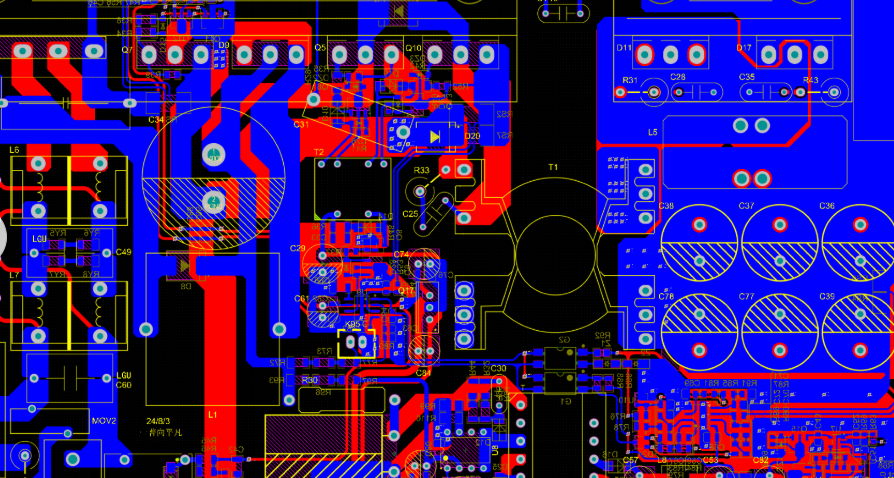

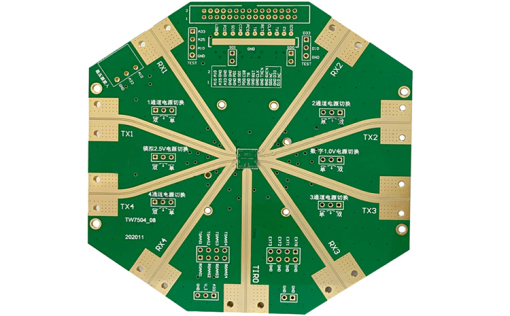

实用案例:时钟线短线布局图解析

以某单片机系统的时钟线布局为例,优化前后对比:

优化前问题

时钟芯片(25MHz)与单片机距离 15cm,布线绕经电源模块,长度达 18cm;

时钟线与 5V 电源线平行布线,间距仅 0.2mm,串扰严重;

延迟约 1.2ns(18cm×0.067ns/cm),超过单片机时序要求的 1ns。

优化后布局(短线策略)

布局调整:将时钟芯片移动至单片机相邻位置,物理距离缩短至 3cm;

布线路径:时钟线从芯片焊盘直接引出,走直线至单片机时钟引脚,长度 3.5cm,延迟 0.23ns;

屏蔽处理:时钟线两侧布置接地过孔,与地平面连接,减少串扰;

DRC 验证:设置时钟线最大长度 5cm,软件未告警,实际测试信号无过冲、振荡。

此案例表明,通过布局优化和短线布线,可将时钟线延迟降低 80%,串扰电压从 150mV 降至 20mV,完全满足设计要求。

设计前先规划走线路径,避免频繁改版

PCB 布线长度过长的危害贯穿电路设计全流程,从信号延迟、反射到电磁干扰,可能导致功能失效、测试失败甚至产品召回。控制长度的核心在于 “设计前期规划”:

布局阶段:按信号流向和功能分区摆放元器件,预估关键线长度,避免后期被迫长线布线;

布线阶段:优先完成高速信号和关键控制线,严格遵循短线原则,利用软件 DRC 实时监控;

验证阶段:结合信号完整性仿真(如 Altium 的 SI 工具),评估长线对时序的影响,提前优化。

只有将 “长度控制” 融入设计全流程,才能从源头减少因布线过长导致的改版,确保产品一次设计成功。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号