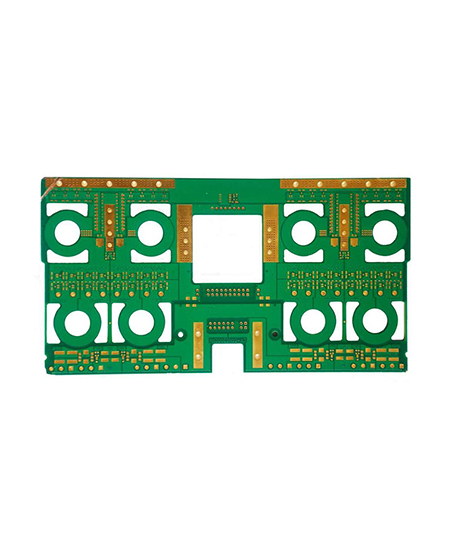

PCB上孤立铜区为什么要控制?如何处理?

在 PCB 设计中,孤立铜区(Isolated Copper Area)是指未与任何电气网络(如电源、地、信号)连接的独立铜箔区域。这类区域看似不影响电路连接,却可能对电路性能、制造工艺和可靠性造成潜在风险。合理控制孤立铜区是提升 PCB 设计质量的重要细节。

孤立铜区可能带来的寄生影响

孤立铜区本质上是 “悬浮” 的导电体,会因自身的物理特性产生寄生效应:

寄生电容:孤立铜区与相邻网络(如信号线、地平面)之间会形成寄生电容,当信号频率较高时,电容的充放电会干扰信号完整性(如增加信号延迟、引入串扰)。

寄生电感:较大的孤立铜区可视为一个感性负载,在高频电路中,其阻抗随频率升高而增大,可能成为电磁辐射的 “发射源” 或 “接收天线”。

电位不确定性:孤立铜区可能因电磁感应产生悬浮电位,当电位积累到一定程度时,可能通过空气或爬电距离放电,干扰附近敏感电路(如模拟信号路径)。

这些寄生效应在低速、简单电路中可能不易察觉,但在高频(≥100MHz)、高灵敏度电路(如射频接收、精密测量)中,可能成为电路失效的隐性诱因。

不良影响:浮地、噪声、制造难题

孤立铜区的不良影响可分为电气性能和制造工艺两类:

电气性能问题

浮地干扰:孤立铜区与地平面之间存在寄生电容,当环境电磁场变化时,会在铜区上感应出浮动电压(即 “浮地”)。这种浮动电压可能通过电容耦合到相邻信号线,导致信号噪声增大。例如,射频电路中 1cm2 的孤立铜区可能引入 - 50dBm 的干扰信号,影响接收灵敏度。

电磁兼容性(EMC)恶化:大面积孤立铜区相当于一个 “无源天线”,会接收外部电磁辐射并重新发射,加剧电磁干扰(EMI)。同时,铜区边缘的电场集中可能产生二次辐射,导致产品无法通过 EMC 测试。

信号完整性下降:高速信号线旁的孤立铜区会改变传输线的特征阻抗(寄生电容导致阻抗降低),引发信号反射和衰减,尤其在差分对附近,可能破坏阻抗匹配。

制造工艺问题

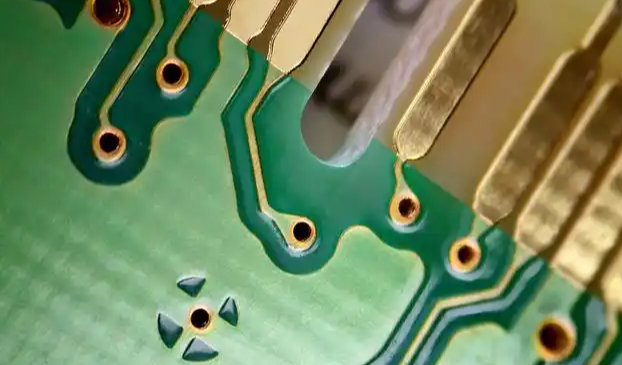

蚀刻不均:孤立铜区在蚀刻过程中,由于周围无连接的铜箔 “牵引”,蚀刻液流动不均匀,可能导致铜区边缘残留(蚀刻不足)或中心过蚀刻(铜箔变薄甚至断裂),影响 PCB 外观和机械强度。

焊接缺陷:若孤立铜区位于焊盘附近,可能因热容量差异导致焊接时温度分布不均,引发虚焊或焊锡桥连。

成本增加:多余的孤立铜区会增加 PCB 的铜箔用量,虽然单块板影响微小,但批量生产时会累积额外成本;同时,制造商可能因处理复杂孤立铜区收取额外费用。

处理方式:连地或去除策略

孤立铜区的处理需根据电路特性和设计需求选择 “连接网络” 或 “直接去除”:

连地策略(推荐优先采用)

将孤立铜区与地网络连接,使其成为地平面的一部分,适用于以下场景:

需要屏蔽的区域:高速信号或敏感电路(如模拟放大器)附近的孤立铜区,可通过细导线(线宽≥0.2mm)或过孔连接至地平面,利用铜区形成局部屏蔽,减少外部干扰。

大面积孤立区:超过 1cm2 的孤立铜区,连接地后可增加地平面的完整性,降低接地阻抗(尤其在双层板中,可补充地平面面积)。

高频电路:高频环境中,连地的铜区可避免成为 “天线”,减少 EMI 辐射。

连接方式:

采用 “星形连接”,通过单根细导线或 1-2 个过孔将孤立铜区与主地平面连接,避免多点连接导致的地环路。

导线需远离敏感信号线,连接点选择铜区边缘而非中心,减少对周边电磁场的扰动。

去除策略

直接删除孤立铜区,适用于以下场景:

小面积孤立区(如<0.1cm2):去除后对电路无明显影响,可简化 PCB 布局。

高密度布线区域:孤立铜区可能阻碍布线或增加设计规则冲突(如间距不足),去除后可释放布局空间。

低频、简单电路:对 EMC 要求不高的电路(如低压小家电控制板),去除孤立铜区可降低制造复杂度。

去除原则:确保去除后不影响相邻网络的铜箔完整性,避免因删除操作导致其他信号线或焊盘受损。

软件自动处理配置

主流 PCB 设计软件均支持自动识别和处理孤立铜区,以 Altium Designer 和 KiCad 为例:

Altium Designer 设置

自动识别孤立铜区:

点击菜单栏 “Tools”→“Copper Pour”→“Pour Manager”,在弹出窗口中勾选 “Detect Isolated Copper”,软件会自动扫描所有铜箔区域,标记孤立部分。

自动处理:

选择 “Remove Isolated Copper”(自动删除):适用于需要完全清除孤立区的场景,删除前建议预览(点击 “Preview”),避免误删有用铜箔。

选择 “Connect to Net”(自动连接至网络):在下拉菜单中选择 “GND” 网络,软件会通过最短路径将孤立区与地连接,导线宽度可在 “Pour Setup” 中设置(推荐 0.2mm)。

KiCad 设置

生成铜箔时排除孤立区:

在铜箔设置界面(“Add Filled Zone”),勾选 “Remove Isolated Islands”,生成敷铜时会自动删除面积小于设定阈值(默认 0.01mm2)的孤立区。

手动处理大孤立区:

点击 “Tools”→“Inspect”→“Find Isolated Copper”,定位大面积孤立区后,手动绘制导线连接至地网络,或使用 “Delete” 工具直接删除。

实例 Demo:孤立区连接地改善信号

以某 433MHz 射频接收电路为例,说明孤立铜区处理前后的效果:

问题场景

PCB 天线附近存在一块 2cm×1cm 的孤立铜区,接收灵敏度测试显示,信号强度波动达 ±5dB,且存在周期性噪声(频率与孤立区共振频率一致)。

处理措施

通过 0.2mm 宽的导线将孤立铜区连接至地平面,导线长度 5mm,连接点位于铜区边缘靠近地平面一侧。

改善效果

信号强度波动降至 ±1dB,噪声幅度从 - 80dBm 降至 - 95dBm,满足通信可靠性要求;

EMC 测试中,30-500MHz 频段的辐射发射降低 10-15dB,顺利通过 CLASS B 限值要求。

原理:连接地后,孤立铜区成为地平面的延伸,消除了其 “天线效应”,同时增强了天线周边的接地连续性,减少信号反射。

优化做牢,易读易制造

孤立铜区的控制是 PCB 设计 “精细化” 的体现,其核心目标是:消除寄生效应、简化制造流程、提升电路可靠性。设计时应遵循 “能连地则连地,无用则去除” 的原则,结合软件自动处理工具,减少人工干预的同时确保处理准确性。

对于高频、高灵敏度电路,需在布局阶段就避免产生大面积孤立铜区(如合理规划敷铜范围);对于低频电路,可通过软件自动删除功能简化设计。最终,经过优化的 PCB 不仅电气性能更稳定,还能降低制造难度和成本,实现 “设计易读、生产易造、性能可靠” 的目标。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号