如何在PCB设计中正确放置去耦电容?

去耦电容是 PCB 电源系统的 “稳压器”,通过抑制电源噪声、补充瞬时电流,为芯片提供稳定的工作电压。其放置方式直接影响去耦效果 —— 即使选用优质电容,若布局不合理,也会因寄生电感增大而失去作用。正确放置去耦电容,是保证电路可靠性的基础设计环节。

去耦电容对供电稳定的重要性

芯片工作时,内部晶体管的开关动作会导致电源电流瞬间变化(如数字芯片的时钟跳变时,电流变化率可达 1A/ns),若电源不能及时补充电流,会引发电源电压波动(即 “电源噪声”)。这种噪声不仅会影响芯片自身工作(如逻辑错误、复位异常),还会通过电源网络传导至其他电路,引发系统性干扰。

去耦电容的核心作用是:在本地存储能量,当芯片需要瞬时大电流时,无需从远处电源传输,直接从电容获取,从而缩短电流路径、降低噪声。实验数据显示,合理放置的去耦电容可将电源噪声从数百毫伏降至几十毫伏,是高速电路(如≥100MHz)稳定工作的必要条件。

放置原则:贴近芯片电源引脚、短路径走线

去耦电容的放置需遵循 “最小化寄生参数” 原则,具体要求如下:

贴近电源引脚

电容应直接放置在芯片的电源引脚(VCC)和接地引脚(GND)附近,距离越近越好,建议距离≤5mm(高速芯片需≤2mm)。

原理:缩短电容与引脚的距离可减少引线的寄生电感(电感量与长度成正比)。例如,5mm 引线的寄生电感约 5nH,而 2mm 引线可降至 2nH,在 100MHz 频率下,前者的阻抗(XL=2πfL)是后者的 2.5 倍,去耦效果显著下降。

操作:在布局阶段,先固定芯片位置,再将去耦电容紧贴其电源引脚摆放,优先占用芯片周围的 “黄金区域”(引脚外侧 1mm 范围内)。

短路径走线

电容与电源引脚、接地引脚的连线需最短、最直,避免绕线或过孔:

布线方式:采用 “菊花链” 或 “星形” 连接,电容的 VCC 端直接连芯片 VCC 引脚,GND 端直接连芯片 GND 引脚,形成 “电容 - 引脚” 的最短回路。

避免过孔:若电容必须跨层接地,需在电容下方就近放置接地过孔(与电容 GND 焊盘距离≤1mm),且过孔数量≥1 个(大电流场景需 2 个),减少过孔带来的寄生电感。

线宽选择:连接导线的线宽应≥0.2mm(1A 电流对应线宽≥0.3mm),确保电流传输通畅,同时避免线宽过宽导致的寄生电容增大。

数量与组合:小电容 + 大容量策略

单一电容难以覆盖宽频率范围的噪声,需采用 “多电容组合” 方案:

电容容值选择

高频去耦:选用 0.1μF(100nF)或 0.01μF(10nF)的陶瓷电容(如 MLCC),负责抑制 10MHz-1GHz 的高频噪声。其寄生电感小(≤1nH),响应速度快,能快速补充瞬时电流。

低频去耦:搭配 1μF-100μF 的电解电容或钽电容,抑制 10kHz-10MHz 的低频噪声,缓解电源的缓慢波动(如负载变化引起的电压跌落)。

组合原则:每个电源引脚至少配 1 个 0.1μF 小电容,每 2-4 个引脚配 1 个 10μF 大电容,形成 “高频 + 低频” 的全频段去耦。

数量确定

简单芯片(如运放、逻辑门):每个电源引脚配 1 个 0.1μF 电容。

复杂芯片(如 MCU、FPGA):主电源引脚(大电流)配 “1 个 0.1μF+1 个 10μF”,辅助电源引脚(小电流)配 1 个 0.1μF,总数量根据引脚数量调整(如 100 引脚 MCU 通常需 10-20 个去耦电容)。

注意:电容并非越多越好,过多会增加 PCB 面积和成本,需通过仿真(如 PSpice 电源噪声分析)优化数量。

特定场景设计建议(双层 / 多层板)

不同层数的 PCB 因结构差异,去耦电容放置需针对性调整:

双层板(无专用地平面)

接地处理:采用 “铺铜接地”,将电容的 GND 焊盘直接与大面积接地铜箔连接,铜箔需尽量宽(≥2mm),模拟 “人工地平面”。

避免跨区:电容应与芯片在同一接地区域,避免 GND 走线跨越电源区域(如 5V 与 3.3V 分区),防止接地噪声耦合。

过孔优化:若必须跨层,在电容 GND 焊盘处放置 2 个以上过孔,并联降低阻抗。

多层板(含电源层 / 地平面)

利用平面优势:电容的 VCC 端通过短引线连电源层,GND 端直接连地平面(无需长导线),借助平面的低阻抗特性增强去耦效果。

过孔布局:在电容与电源层之间仅用 1 个过孔,减少寄生电感;地平面过孔与电容 GND 焊盘直接相连,形成 “电容 - 地平面” 的低阻抗回路。

分区去耦:不同电压域(如 1.8V、3.3V)的去耦电容需分区域放置,避免跨域干扰,电容的 GND 应连接至对应电压域的地平面(或通过 0Ω 电阻单点连接主地)。

实例分析与布局示意图

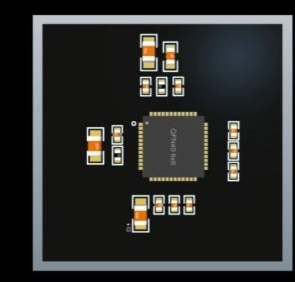

以 STM32F103(ARM Cortex-M3 单片机)为例,其电源引脚分布及去耦电容布局如下:

芯片引脚情况:包含 VDD(3.3V 主电源,4 个引脚)、VDDA(模拟电源,1 个引脚)、VSS(接地,5 个引脚)。

电容配置:

每个 VDD 引脚旁放置 1 个 0.1μF 陶瓷电容(0402 封装),共 4 个;

VDDA 引脚旁放置 1 个 0.1μF 陶瓷电容 + 1 个 1μF 钽电容(抑制模拟噪声);

在芯片对角处放置 1 个 10μF 电解电容(负责全局低频去耦)。

布局特点:

0.1μF 电容与 VDD 引脚的距离均≤2mm,采用 “直连” 布线(无拐角);

电容 GND 焊盘直接连地平面,通过 1 个过孔与内层地连接;

10μF 电容位于电源输入口附近,与主电源路径串联,过滤外部引入的低频噪声。

(示意图描述:芯片居中,4 个 0.1μF 电容分别紧贴 4 个 VDD 引脚,呈 “对称分布”;VDDA 引脚旁的电容与模拟电路区相邻;10μF 电容位于 PCB 电源接口与芯片之间的路径上。)

布局精细决定电源质量

去耦电容的放置是 “细节决定成败” 的典型案例 —— 其效果不仅取决于电容参数,更依赖布局的精细度。核心原则可概括为:“近、短、直、多”(近引脚、短路径、直布线、多组合)。

设计时需将去耦电容布局纳入前期规划,与芯片布局同步进行,而非后期 “补位”。通过仿真验证(如使用 Altium 的 Power Integrity 工具)优化位置和数量,最终实现电源噪声≤5%(芯片手册通常要求),为电路稳定工作奠定基础。记住:优质的电源是芯片性能的 “基石”,而去耦电容的布局则是 “基石” 的关键支撑。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号