信号完整性(SI)是多层 PCB 叠层设计的核心指标,直接影响高速信号的传输质量。随着数据速率从 1Gbps 向 100Gbps 突破,叠层设计需解决阻抗匹配、串扰、时延等问题。通过合理规划层间结构与布线参考平面,可将信号完整性指标提升 30-50%。

特征阻抗(Z0)是高速信号传输的基础参数(通常为 50Ω/75Ω),其值由叠层物理参数决定:

阻抗计算公式:微带线(信号层在表层)Z0=87/√(εr+1.41)×ln (5.98h/(0.8w+t));带状线(信号层在中间)Z0=60/√εr×ln (4h/(0.67π(w+0.8t)))。其中 εr 为介电常数,h 为信号层到参考平面距离,w 为线宽,t 为铜厚。

关键参数控制:① 线宽与间距:50Ω 微带线(FR-4,h=0.15mm)线宽约 0.2mm,间距需≥3 倍线宽(避免串扰);② 介质厚度:误差需<10%(否则阻抗偏差>5%),例如设计 h=0.2mm 时,实际需控制在 0.18-0.22mm;③ 介电常数:高频材料(如 RO4350)的 εr 稳定性更好(随频率变化<2%),适合 10Gbps 以上信号。

叠层设计策略:高速信号层需紧邻参考平面(h≤0.2mm),且参考平面必须完整(无分割)。例如,PCIe 4.0(16Gbps)信号层与 GND 层的间距需控制在 0.12-0.15mm,阻抗偏差<5%(47.5-52.5Ω)。

串扰(Crosstalk)是相邻信号线间的不期望耦合,叠层设计可从根源减少串扰:

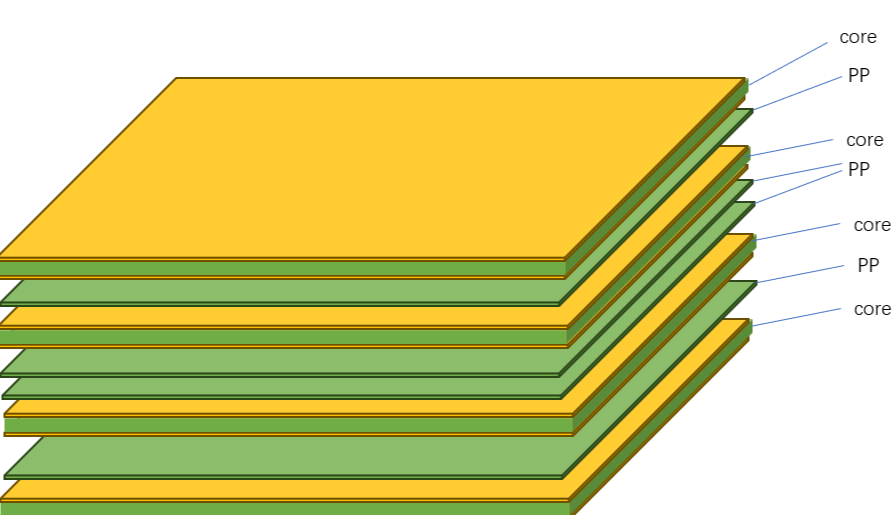

层间串扰控制:信号层之间需插入接地层(或电源层),层间距≥0.2mm(FR-4 中,间距每增加 0.1mm,层间串扰降低 6dB)。例如,6 层板中信号层 2 与信号层 3 之间插入 VCC 层,可将串扰从 - 30dB 降至 - 40dB 以下(符合 PCIe 规范)。

同层串扰控制:通过叠层规划减少同层信号密度 —— 高速信号层的布线密度应<50%(每英寸线数<20),差分对间距≥3 倍线宽(差分对内距通常为线宽的 1-1.5 倍)。DDR4 信号层建议单独设置,避免与其他高速信号同层(可减少 50% 同层串扰)。

参考平面连续性:信号布线下方的参考平面(GND/VCC)需完整,避免跨分割(Split Plane)。若必须跨分割,需在分割处加桥接电容(100nF)并控制跨线长度<5mm(否则串扰增加 10-20dB)。

高速并行总线(如 DDR、LVDS)对信号时延(Delay)和时延差(Skew)要求严苛,叠层设计需重点控制:

时延计算与控制:信号时延主要由介质厚度和介电常数决定,公式为 Delay=√εr×h×1.016(ns/m)。FR-4 中 0.2mm 厚介质的时延约 66ps/inch,罗杰斯材料(εr=3.48)可降至 55ps/inch(减少 17%)。叠层设计中,同一总线的信号需走同一层(介质相同),确保时延一致性。

Skew 控制策略:① 层间 skew:不同层的信号时延差需<10ps(如 DDR4 的 tDQSS 要求),可通过调整介质厚度补偿(如将一层 h 设为 0.18mm,另一层设为 0.22mm,平衡时延);② 同层 skew:通过等长布线(误差<50mil)控制,叠层设计需预留足够布线空间(同层线长差<100mil)。

温度对时延的影响:温度升高会导致介电常数微小变化(FR-4 每℃变化 0.02%),叠层设计应选择低温度系数材料(如 PTFE,变化率<0.01%/℃),或在仿真中加入温度补偿系数。

不同类型信号的电磁兼容性差异大,叠层设计需物理隔离:

数字与模拟信号隔离:模拟信号层(如 ADC 输入)与数字信号层之间必须用完整接地层隔离,垂直距离≥0.3mm(形成法拉第笼)。模拟地(AGND)与数字地(DGND)在电源层通过 0Ω 电阻或磁珠单点连接,避免地环路干扰(模拟信号噪声降低 20-30mV)。

射频与低频信号隔离:射频信号(>1GHz)需单独层,周围用接地铜皮包围(隔离带宽度≥2 倍线宽),层间距离≥0.5mm(减少对其他层的辐射)。射频层下方的接地层需完整(无过孔),避免能量泄漏(插入损耗降低 10dB 以上)。

高功率与低功率信号隔离:功率电路(>1A)的布线层需远离低功率信号层(如传感器信号),中间用接地层隔离,且功率层的铜厚需≥35μm(降低发热导致的温度梯度,减少对邻近信号的热影响)。

叠层设计需通过仿真验证,确保满足信号指标:

仿真流程:① 建立叠层模型(输入各层厚度、材料参数);② 提取阻抗剖面(检查各信号层的阻抗是否在目标范围);③ 串扰仿真(注入 1V 信号,测量相邻线的耦合噪声);④ 眼图仿真(评估高速信号的眼高、眼宽是否达标)。

关键指标标准:① 阻抗:50Ω±5%(高速数字)、75Ω±5%(射频);② 串扰:近端串扰(NEXT)<-25dB,远端串扰(FEXT)<-30dB;③ 眼图:眼高>50% Vpp,眼宽>0.5UI(单位间隔)。

叠层调整策略:若仿真发现阻抗偏低(如 45Ω),可增加信号层到参考平面的距离(h 从 0.15mm 增至 0.18mm);串扰超标时,增加层间距或减少同层布线密度。某案例中,通过将 6 层板的信号层间距从 0.2mm 增至 0.3mm,串扰从 - 28dB 降至 - 35dB,满足 PCIe 3.0 要求。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号