高速PCB电镀通孔设计终极指南

如果您正在设计高速印刷电路板 (PCB),掌握电镀通孔 (PTH) 设计对于确保信号完整性和性能至关重要。PTH 过孔连接 PCB 的不同层,但在高速应用中,如果设计不当,它们可能会带来阻抗不匹配和信号延迟等挑战。

什么是电镀通孔 (PTH),为什么它们在高速 PCB 中很重要?

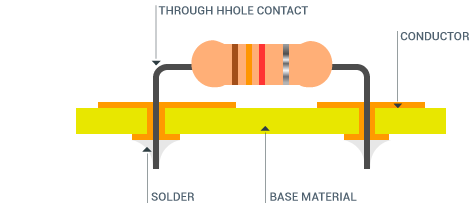

电镀通孔是在 PCB 上钻出的小导电孔,用于在层之间建立电气连接。与非电镀孔不同,PTH 内部镀有一层薄薄的镀铜层,确保可靠的导电性。在高速 PCB 中,信号传输的频率通常超过 1 GHz,PTH 过孔在维持信号质量方面发挥着关键作用。设计不当的 PTH 会导致反射、串扰和信号丢失,从而导致系统故障。

在高速设计中,包括过孔在内的每个元素都会影响性能。必须仔细规划 PTH 过孔,以尽量减少对信号路径的干扰。让我们探讨如何通过关注阻抗控制、信号完整性和布线策略等关键方面来有效地设计它们。

高速PCB的关键PTH设计规则

为高速 PCB 设计 PTH 过孔需要遵守特定规则以避免性能问题。以下是要遵循的最重要的准则:

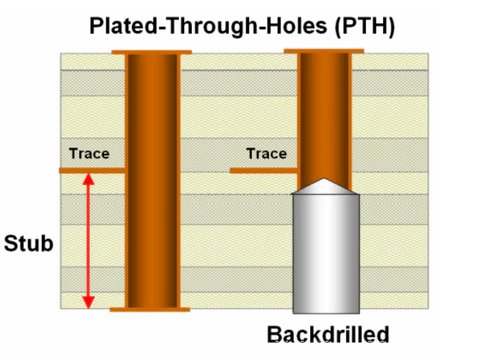

1. 最小化过孔短截线长度

在高速设计中,过孔短截线(信号转换为另一层后过孔的未使用部分)充当天线,导致信号反射。对于工作频率为 5 GHz 的信号,长度超过 0.5 mm 的短截线可能会引入显着的噪声。如果您的设计允许,使用背钻去除未使用的短截线部分,或者选择盲孔和埋孔。

2. 优化过孔直径和焊盘尺寸

较小的过孔直径可减少寄生电容和电感,这对于在高频下保持信号完整性至关重要。高速设计的典型通孔直径范围为 0.2 mm 至 0.3 mm,焊盘尺寸约为 0.5 mm 至 0.6 mm。确保过孔尺寸支持载流能力,同时最大限度地减少信号失真。

3. 战略性地放置过孔

除非必要,否则避免将 PTH 过孔直接放置在高速信号的路径中。如果需要过孔,请将其定位以尽量减少走线长度中断。例如,将过孔放置在走线的末端而不是中间可以减少信号路径中断。

高速设计中PTH的阻抗控制

阻抗控制是高速PCB设计的基石,如果管理不当,PTH过孔可能会破坏信号路径的特性阻抗。以下是确保使用 PTH 进行阻抗控制的方法:

1. 通过阻抗匹配走线阻抗

高速信号通常需要受控阻抗,例如单端走线为 50 欧姆,差分对为 100 欧姆。PTH 过孔引入电感和电容,从而改变阻抗。为了解决这个问题,请调整过孔焊盘尺寸和反焊盘(接地层中过孔周围的间隙区域)。对于 50 欧姆走线,0.8 mm 至 1.0 mm 的反焊盘直径通常效果很好,尽管仿真工具可以为您的叠层提供精确的值。

2. 使用接地过孔作为返回路径

将接地过孔放置在高速信号过孔附近,以提供低阻抗返回路径。这降低了环路电感并最大限度地减少了电磁干扰 (EMI)。一种常见的做法是为1 mm半径内的每个信号过孔放置一个接地过孔。

3. 模拟通孔效果

使用电磁仿真软件对设计中PTH过孔的阻抗进行建模。工具可以预测过孔如何影响 1 GHz 以上频率下的信号行为,允许您在制造前调整过孔间距和焊盘尺寸等参数。

通过电镀通孔确保信号完整性

信号完整性是指信号在通过 PCB 传输时保持信号质量。如果设计不当,PTH 过孔会降低信号完整性。以下是在高速设计中保持信号完整性的策略:

1. 通过适当的间距减少串扰

当相邻过孔中的信号相互干扰时,就会发生串扰。为防止这种情况发生,请在高速信号过孔之间保持至少三倍的最小间距。例如,对于通孔直径为 0.3 mm,间距保持为 0.9 mm 或更大。

2. 避免关键网络中的过孔转换

每次信号通过过孔过渡到另一层时,它都会遇到阻抗不连续性。限制关键高速网络的过孔转换数量。如果过渡不可避免,请确保过孔被实心接地层包围,以尽量减少噪声。

3.使用优质材料

PCB 的介电材料会影响信号在 PTH 过孔周围的行为方式。介电常数 (Dk) 为 3.0 至 3.5 的低损耗材料是 10 GHz 以上频率的理想选择,因为它们可以减少过孔附近的信号衰减。

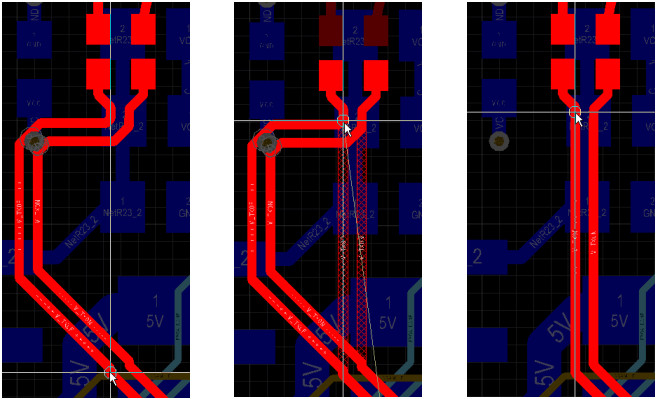

高速 PCB 中带有 PTH 的差分对布线

差分对通常用于 USB、PCIe 和以太网等协议的高速设计,其中两个信号携带互补数据以降低噪声。通过PTH过孔布线差分对需要精度以保持信号平衡和时序。以下是正确作的方法:

1. 保持差分过孔对称

将差分对的过孔尽可能靠近放置,同时保持对称性。间距不均匀会导致偏斜,即一个信号先于另一个信号到达,从而扰乱时序。差分过孔之间的间距为 0.5 mm 至 0.8 mm,通常适用于高达 5 GHz 的信号。

2. 匹配过孔前后的走线长度

差分对中的长度不匹配会导致相位差,从而降低性能。确保过孔两侧的走线长度相等。如果由于过孔放置而必须延长一条走线,请使用蛇形布线以匹配 0.1 mm 以内的长度。

3. 用接地层包围差分过孔

为了屏蔽差分对免受外部噪声的影响,请在差分对周围放置接地过孔。这创造了一个受控环境,减少了 EMI 和串扰。差分对过孔周围有四到六个接地过孔环是 3 GHz 以上信号的常见做法。

高速 PCB 过孔和 PTH 设计的高级技巧

除了基础知识之外,以下是一些进一步优化高速 PCB 中 PTH 设计的高级策略:

1. 使用盲孔和埋孔

盲孔(将外层连接到内层)和埋孔(仅连接内层)消除了短截线,从而提高了信号完整性。虽然这些过孔增加了制造成本,但对于工作在 10 GHz 以上的设计来说,它们值得考虑。

2. 实现接地层的过孔缝合

过孔缝合涉及在高速信号路径周围放置多个接地过孔,以创建稳健的返回路径。该技术在多层板中特别有用,其中信号可以通过 PTH 过孔穿过多层。以 λ/10 的间隔(其中 λ 是最高信号频率的波长)进行空间缝合过孔以抑制谐振。

3. 测试和验证设计

设计 PCB 后,使用时域反射计 (TDR) 测量由 PTH 过孔引起的阻抗不连续性。此测试有助于在全面生产之前识别反射或不匹配等问题,从而节省时间和成本。

高速 PCB 的 PTH 设计中应避免的常见错误

即使是经验丰富的设计人员在高速应用中使用 PTH 过孔时也可能会出错。以下是一些需要注意的陷阱:

忽略 via 存根:未能解决短截线可能会导致严重的信号反射,尤其是在 1 GHz 以上的频率下。

过孔过度拥挤:将过孔靠近放置会增加串扰并使布线复杂化。

忽略接地层:如果过孔附近没有实心接地层,返回路径会变长,从而增加电感和 EMI。

跳过模拟:不模拟通孔效果可能会导致意外的性能问题,这些问题在制造后修复成本很高。

掌握 PTH 设计以实现高速 PCB 的成功

电镀通孔设计是高速 PCB 开发的一个关键方面。通过遵循 PTH 设计规则、专注于阻抗控制、确保信号完整性和优化差分对布线,您可以创建即使在最高频率下也能可靠运行的电路板。请记住尽量减少过孔存根,使用接地过孔作为返回路径,并模拟您的设计以及早发现问题。通过这些策略,您将有能力应对高速 PCB 设计的挑战并提供一流的结果。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号