最大走线间距对信号完整性的影响

在高速 PCB 设计领域,保持信号完整性对于确保可靠性能至关重要。直接影响信号完整性的一个关键因素是走线间距。但是,最大走线间距如何影响信号完整性呢?简而言之,走线间距会影响印刷电路板 (PCB) 中的串扰、阻抗控制和整体信号质量。当走线间距太近时,干扰和噪声会降低信号质量,而间距过大会导致布局效率低下和其他设计挑战。

了解 PCB 设计中的走线间距

走线间距是指 PCB 上两条导电走线之间的距离。这些走线在组件之间传输电信号,它们的间距对这些信号的行为方式起着至关重要的作用。在高速 PCB 设计中,信号以高于 100 MHz 的频率切换,即使是走线间距的微小变化也会导致严重问题。

管理走线间距的主要目标是最大限度地减少干扰,同时保持紧凑高效的布局。如果走线太近,来自一条走线的电磁场会干扰另一条走线,从而导致一种称为串扰的现象。另一方面,走线间距太远会不必要地增加电路板尺寸,从而增加成本并使布线复杂化。

信号完整性:可靠 PCB 性能的基础

信号完整性是指电信号通过 PCB 时的质量。具有良好完整性的信号可以保持其形状、时序和幅度,而不会出现失真或噪声。信号完整性差可能会导致数据错误、时序问题和系统故障,尤其是在 USB、HDMI 或 DDR 内存接口等高速应用中。

有几个因素会影响信号完整性,包括走线长度、阻抗失配和电磁干扰 (EMI)。走线间距尤为重要,因为它直接影响串扰和阻抗控制——这是高速设计中的两个关键要素。

走线间距如何影响 PCB 中的串扰

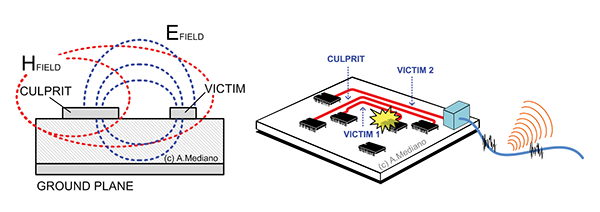

当一条走线上的信号由于电磁耦合而在附近的走线上感应出不需要的信号时,就会发生串扰。这种干扰会损坏数据并降低性能,尤其是在高速电路中。走线越近,耦合越强,串扰风险越高。

例如,在运行频率为 1 GHz 的并联走线的设计中,将间距从 10 密耳(0.254 毫米)减小到 5 密耳(0.127 毫米)可以增加高达 20-30% 的串扰,具体取决于介电材料和走线长度。为了缓解这种情况,设计人员通常遵循“3W规则”,即走线之间的间距应至少为走线宽度的三倍,以将串扰减少到可接受的水平。

但是,最大走线间距并不总是解决方案。虽然增加间距可以减少串扰,但它可能会导致更大的电路板尺寸和布线挑战。取得平衡是关键,仿真工具可以帮助根据特定的间距值预测串扰水平。

走线间距和阻抗控制:关键连接

阻抗控制是高速 PCB 设计的另一个重要方面,可确保信号传输时没有反射或损耗。走线的特性阻抗取决于其宽度、厚度、与相邻走线或平面的间距以及电路板材料的介电常数。对于 USB 3.0 (5 Gbps) 中的高速信号,保持一致的阻抗(单端信号通常为 50 欧姆,差分对为 100 欧姆)至关重要。

走线间距会影响阻抗,尤其是在差分对布线中。如果差分对中两条走线之间的间距过大,阻抗就会增加,导致失配,从而导致信号反射。例如,目标阻抗为 100 欧姆的差分对可能需要在介电常数为 4.2 的标准 FR-4 材料上间隔 8 密耳(0.203 毫米)。将间距增加到 12 密耳(0.305 毫米)可能会将阻抗提高到 110 欧姆,从而引入反射并降低信号完整性。

设计人员必须使用阻抗计算器或仿真软件来确定适合其特定叠层和信号要求的最佳走线间距。层叠层设计也发挥着作用,因为与参考平面(接地或电源)的间距会影响阻抗以及走线到走线的间距。

高速PCB设计中最大走线间距的挑战

虽然增加走线间距可以减少串扰并有助于阻抗控制,但将走线间距推到最大并不总是实用或有益的。以下是与高速 PCB 设计中最大走线间距相关的一些挑战:

增加电路板尺寸:更宽的间距意味着走线占用更多的空间,从而导致更大的电路板。这可能会增加制造成本,并且对于智能手机或物联网模块等紧凑型设备可能不可行。

路由复杂性:高速设计通常涉及密集的元件放置。过大的间距会使走线的有效布线变得更加困难,尤其是在空间有限的多层板中。

信号时序问题:在差分对或匹配长度走线中,过大的间距可能会引入偏斜,即一个信号稍微先于另一个信号到达,从而导致时序误差。例如,在 10 Gbps 时,由于间距而导致的 1 mil (0.0254 mm) 长度不匹配可能会导致约 6 皮秒的时序偏差,这对于如此高的速度来说非常重要。

设计人员在决定走线间距时必须权衡这些权衡。通常,中间立场——平衡信号完整性的间距与实际的布局限制——是最好的方法。

在高速设计中优化走线间距的最佳实践

为了在管理走线间距的同时实现最佳信号完整性,请考虑以下专为高速 PCB 设计量身定制的最佳实践:

遵循行业准则:使用既定规则(例如 3W 间距规则)以尽量减少串扰。对于差分对,请遵守基于目标阻抗的间距建议(例如,FR-4 上的 100 欧姆差分阻抗为 8-10 密耳)。

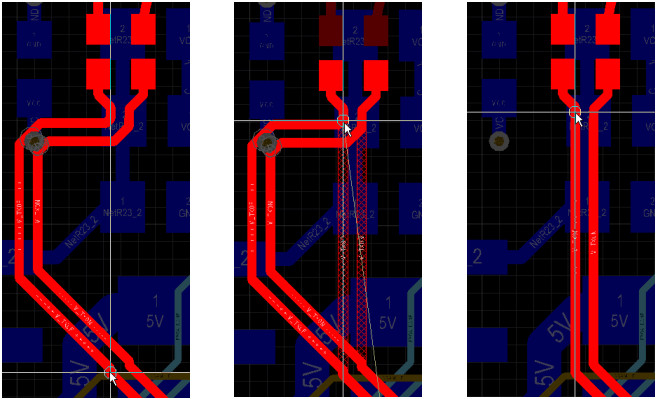

使用模拟工具:利用具有内置信号完整性分析功能的 PCB 设计软件,根据走线间距模拟串扰和阻抗。迭代调整间距以找到设计的最佳位置。

优先考虑接地层:信号走线下方的实心接地层可以通过为电磁场提供返回路径来减少串扰。保持信号层和接地层之间的间距一致,以保持阻抗。

首先路由高速信号:在其他走线之前规划关键高速信号的布线,以确保足够的间距并最大限度地减少干扰。将相似的信号组合在一起,同时保持间距以避免耦合。

考虑材料特性:PCB 材料的介电常数 (Dk) 会影响阻抗和串扰。对于高速设计,Rogers 或 Isola 等低 Dk 材料可以在不牺牲信号完整性的情况下实现更紧密的间距。

实际应用:走线间距的实际应用

让我们看一个实际示例,看看走线间距如何影响现实场景中的信号完整性。考虑为运行频率为 5 GHz 的 3.5G 通信模块设计的 PCB。在如此高的频率下,信号完整性对于避免数据丢失或误码至关重要。

在此设计中,关键走线是目标阻抗为 100 欧姆的数据传输差分对。在 FR-4 材料上使用标准 4 层叠层,最佳走线宽度计算为 6 密耳(0.152 毫米),对之间的间距为 8 密耳(0.203 毫米)。相邻走线的间距设置为 18 密耳(0.457 毫米),以遵循 3W 规则(走线宽度的 3 倍)。仿真结果表明,串扰低于-30 dB,阻抗保持在目标的±5%以内,确保了可靠的性能。

如果差分对之间的间距增加到 12 密耳(0.305 毫米),阻抗会上升到 108 欧姆,从而导致反射,从而降低信号质量。相反,将相邻走线的间距减小到 10 mils (0.254 mm) 会将串扰增加到 -20 dB,从而引入噪声。此示例强调了高速 PCB 设计所需的走线间距的微妙平衡。

管理迹线间距的高级技术

对于复杂的设计,标准间距规则可能不够。以下是进一步优化走线间距和信号完整性的先进技术:

守卫痕迹:在高速信号走线之间放置接地走线以充当屏蔽层,减少串扰。确保这些防护走线在多个点接地以发挥作用。

交错路由:避免长距离运行并行走线。相反,以 90 度角交错或交叉走线,以尽量减少耦合。

控制介电厚度:与您的制造商合作控制层之间的介电厚度,因为这会影响阻抗和串扰以及走线间距。

这些技术需要仔细规划并经常与制造合作伙伴合作,以确保可行性和成本效益。

通过迹线间距取得适当的平衡

走线间距是高速 PCB 设计中保持信号完整性的关键因素。它直接影响串扰、阻抗控制和整体性能。虽然最大走线间距可以减少干扰,但它通常会带来权衡,例如增加电路板尺寸和布线挑战。通过遵循最佳实践、利用仿真工具并考虑材料特性,设计人员可以优化走线间距,以实现可靠的信号完整性,而不会影响布局效率。

了解走线间距和信号完整性之间的关系对于应对现代电子产品(从 5G 模块到高速数据接口)的挑战至关重要。通过仔细的规划和正确的设计策略,您可以确保您的 PCB 发挥最佳性能,满足当今快节奏的技术环境的需求。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号