电源完整性设计中去耦电容的布局原则有哪些?

电源完整性(PI)是高速PCB设计的核心挑战之一,而去耦电容是抑制电源噪声的关键器件。在高速数字电路中(如FPGA、处理器),瞬时开关电流(ΔI/Δt)通过电源分配网络(PDN)的寄生电感(L)会产生噪声电压(\(V_{noise} = L \times ΔI/Δt\)),导致芯片供电电压波动,影响逻辑电平识别。本文将从去耦电容的工作原理出发,详细阐述布局的核心原则、工程化策略及仿真验证方法。

二、去耦电容的工作原理

1. 三大作用

? 高频旁路:为IC开关电流提供低阻抗回流路径(频率范围:10MHz-1GHz);

? 储能缓冲:补偿VRM(电压调节模块)响应延迟,维持瞬时电流需求;

? 抑制谐振:抵消电源平面的寄生电感,降低PDN阻抗尖峰。

2. 等效电路模型

去耦电容并非理想器件,其等效电路为:\(C_{decouple} + ESL(等效串联电感) + ESR(等效串联电阻)\)。其中,ESL是布局关键控制参数(典型0402封装ESL≈0.5nH,0603封装≈1.2nH)。

三、核心布局原则

1. 靠近IC电源引脚(≤100mil)

? 原理:缩短电容与IC引脚的路径长度,降低ESL(路径电感\(L \propto \ln(l)\),\(l\)为路径长度)。

? 工程要求:

? 电容焊盘到IC电源引脚的走线长度≤100mil(2.54mm);

? 优先采用“电容-过孔-电源平面”直连结构,避免绕线。

? 反面案例:某FPGA电源引脚与去耦电容间距200mil,ESL增至1.8nH,导致100MHz处PDN阻抗上升至50mΩ(目标阻抗20mΩ),电源噪声超标。

2. **多容值组合,覆盖宽频噪声**

? 容值选择:按“10倍频法则”搭配,如0.1μF(100MHz)+10nF(1GHz)+1nF(10GHz),覆盖10MHz-10GHz噪声频段。

? 布局顺序:小容值电容(高频)最靠近引脚,大容值(低频)次之。例如:

? 0402封装1nF(ESL最小)贴IC引脚;

? 0603封装10nF紧邻其外侧;

? 0805封装0.1μF放在最外层。

3. **电源-地平面紧邻,减少平面电感**

? 结构要求:去耦电容下方需为完整电源/地平面对,且平面间距≤50mil(介质厚度H越小,平面电容\(C \propto 1/H\)越大)。

? 反焊盘优化:电容过孔反焊盘直径=2×孔径+0.2mm,避免平面分割导致回流路径加长。

4. **避免“孤岛”和“瓶颈”**

? 孤岛效应:电容过孔周围电源平面被过多信号过孔切割(反焊盘重叠),形成电流“孤岛”,需保证电容到IC的回流路径宽度≥2mm。

? 瓶颈效应:电源平面狭窄通道(如BGA下方)导致电流密度过高(>5A/mm2),需增加过孔数量(按1A/过孔计算,如10A电流需10个过孔)。

5. **与IC封装协同设计**

? BGA封装:电容优先放置在BGA焊盘投影区域外(避免与引脚冲突),采用“菊花链”布局(多个电容并联)降低总ESL。

? QFN封装:利用暴露焊盘(Exposed Pad)直接连接地平面,电容地端就近连接暴露焊盘(路径长度≤50mil)。

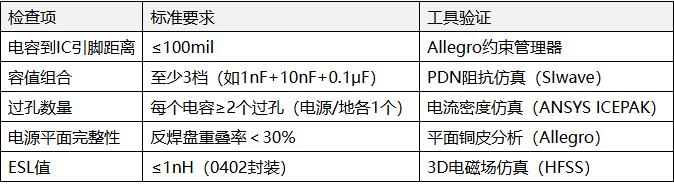

四、布局检查清单

五、仿真与验证

1. PDN阻抗仿真(SIwave)

? 目标:在IC工作频率范围内(如1MHz-2GHz),PDN阻抗<目标阻抗(\(Z_{target} = ΔV / ΔI\),ΔV为电压纹波容限,ΔI为最大瞬态电流)。

? 案例:某处理器内核电压1.0V(ΔV=±5%=50mV),ΔI=10A,目标阻抗\(Z_{target}=50mV/10A=5mΩ\)。通过优化去耦电容布局(0402封装1nF×8并联,ESL=0.3nH),PDN阻抗在100MHz处从25mΩ降至4.8mΩ(达标)。

2. 时域噪声测试

? 工具:示波器+电流探头(如Tektronix TCP0030);

? 测试点:IC电源引脚处(通过PCB测试点);

? 标准:噪声峰峰值≤5%VCC(如1.0V电源≤50mV)。

六、工程误区与解决方案

1. 误区:电容数量越多越好

? 问题:过多电容导致布局拥挤,过孔数量增加,反而分割电源平面,增加ESL。

? 方案:通过PDN仿真确定最小电容数量(如某DDR4电源,8个0.1μF+4个10nF即可满足阻抗要求)。

2. 误区:忽略电容封装差异

? 问题:0805封装电容ESL(1.5nH)比0402(0.5nH)大3倍,高频去耦效果差。

? 方案:高频段(>500MHz)优先0402或0201封装,低频段(<100MHz)用0805或1206封装。

去耦电容布局的核心是“最小化ESL、优化回流路径”,需结合IC需求(瞬态电流、工作频率)、封装类型(BGA/QFN)、PDN结构(电源平面厚度、介质材料)综合设计。通过“仿真驱动布局+测试验证”流程,可有效抑制电源噪声,保障高速电路稳定工作。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号