PCB叠层结构对信号完整性的影响及优化方法?

一、引言

PCB叠层结构是高速信号传输的“地基”,直接影响阻抗控制、串扰抑制、电源完整性及EMC性能。在高频高速设计中(如10Gbps以上),不合理的叠层会导致信号反射、串扰超标、电源噪声增大等问题。

二、叠层设计核心目标

1. 阻抗控制:为高速信号提供稳定的参考平面(电源/地),确保特性阻抗(如50Ω单端、100Ω差分)偏差≤±10%。

2. 串扰抑制:通过地层隔离敏感信号层,降低层间串扰(目标:近端串扰NEXT<-30dB@1GHz)。

3. 电源完整性:提供低阻抗电源分配网络(PDN),平面电容(\(C = \varepsilon0 \varepsilonr A / h\))越大,PDN阻抗越低。

4. EMC优化:对称结构减少辐射,完整地平面降低共模噪声。

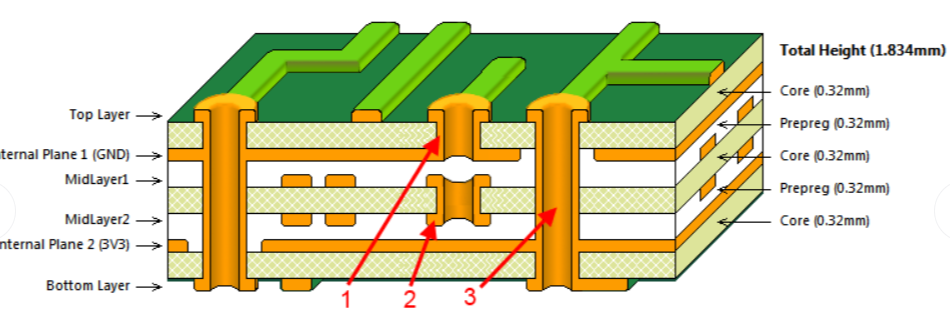

三、经典叠层结构(4-12层)

1. 4层板(低成本通用)

? 结构:Signal1(顶层)-GND-Power-Signal2(底层)

? 适用场景:低速数字电路(≤500MHz)、小尺寸PCB(如传感器模块)。

? 局限性:

? 信号层无相邻地平面,阻抗控制困难(偏差±15%);

? 电源/地层间距大(通常≥0.4mm),平面电容小(PDN阻抗高)。

2. 6层板(高速通用)

? 结构:Signal1-GND-Signal2-Power-GND-Signal3

? 优势:

? 顶层/底层信号有相邻地平面(微带线阻抗易控);

? 内层Signal2为带状线(上下地平面,串扰低);

? 两个地平面(GND1、GND2)抑制辐射。

? 适用场景:1-10Gbps信号(如USB3.0、DDR4)。

3. 8层板(高性能高速)

? 结构:Signal1-GND1-Power1-Signal2-Signal3-Power2-GND2-Signal4

? 优化点:

? Power1/Power2分离(如1.8V/3.3V),避免电源噪声耦合;

? Signal2/Signal3为带状线(差分阻抗100Ω±5%);

? GND1/GND2通过过孔缝合(Via Stitching),降低共模辐射。

? 适用场景:25Gbps SerDes(如PCIe5.0)、多电源系统。

4. 12层板(复杂高速)

? 结构:Signal1-GND1-Signal2-Power1-GND2-Signal3-Signal4-GND3-Power2-Signal5-GND4-Signal6

? 特点:

? 独立GND平面隔离各信号层;

? 内层Power1/Power2采用厚铜(2oz),降低IR Drop;

? 支持多组差分对(如4路PCIe6.0×16)。

四、高速信号层规划原则

1. 微带线vs带状线

? 微带线(表层):

? 结构:信号层+相邻地平面(介质厚度H);

? 优势:成本低(无需内层),散热好;

? 局限:受环境干扰(EMI辐射大),阻抗受阻焊影响(绿油厚度导致Dk变化)。

? 适用:低速信号、测试点引出。

? 带状线(内层):

? 结构:信号层夹在两个地/电源平面之间;

? 优势:阻抗稳定(±5%),串扰低(相邻层隔离),EMI辐射小;

? 适用:高速差分信号(如USB4、SATA)、时钟信号。

2. 关键信号优先级

信号类型 | 推荐层类型 | 参考平面 | 间距要求 |

时钟信号(>1GHz) | 内层带状线 | GND | 与其他信号间距≥5W |

差分对(≥10Gbps) | 内层带状线 | GND | 等长差≤5mil |

电源总线(大电流) | 内层平面 | GND | 铜厚≥2oz |

低速IO信号 | 顶层/底层 | Power/GND | 无特殊要求 |

3. 跨层信号处理

? 过孔数量:高速信号换层过孔≤2个(每个过孔引入~0.5nH电感);

? 参考平面连续:避免信号跨电源分割(如从GND1到GND2需通过GND过孔桥接);

? 背钻(Back Drilling):去除过孔残桩(Stub),如10Gbps信号要求Stub≤5mil(减少反射)。

五、工程优化案例:6层板叠层优化

1. 原始问题:

某6层板(结构:Sig1-GND-Sig2-Power-GND-Sig3),DDR4信号(2400Mbps)串扰超标(NEXT=-25dB@1.2GHz)。

2. 优化措施:

? 调整层间距:GND-Sig2间距从0.2mm减小到0.1mm(Sig2阻抗从50Ω→52Ω,更稳定);

? Sig2/Sig3正交布线:避免平行走线(串扰降低至-35dB);

? Power平面分割:将Power层分为1.8V和3.3V,减少电源噪声耦合。

3. 验证结果:

? 阻抗控制:±8%(原始±15%);

? 串扰:NEXT=-38dB@1.2GHz(达标);

? 电源噪声:1.8V电源纹波≤30mV(原始50mV)。

六、叠层设计工具与流程

1. 阻抗计算:Polar SI9000(微带线/带状线阻抗公式);

2. 信号完整性仿真:HyperLynx LineSim(串扰、反射预测);

3. PDN分析:SIwave(电源平面阻抗、谐振频率);

4. EMC仿真:ANSYS HFSS(辐射场强预测)。

高速PCB叠层设计需遵循“参考平面优先、信号分层隔离、电源完整性兼顾”原则;

? 层数选择:根据信号速率(10Gbps→≥6层)、电源种类(多电源→≥8层);

? 阻抗控制:微带线关注H(介质厚度),带状线关注B(上下介质总厚度);

? 验证工具:通过仿真提前预测阻抗、串扰、电源噪声,避免后期改版。

合理的叠层是高速信号完整性的“第一道防线”,需在设计初期投入足够资源规划。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号