PCB测试验证技术:物理层的质量把关

信号完整性测试是验证设计质量的最终环节,通过物理测量评估实际 PCB 的信号传输性能。测试技术主要分为时域测量(眼图、TDR)和频域测量(S 参数)两大类,分别反映信号的时域特性和频率响应特性。遵循 IEEE 1149.4 和 IPC-TM-650 等标准进行测试,可确保测量结果的准确性和可比性。

眼图测试是评估高速信号质量的核心方法。测试设备通常采用带宽至少为信号速率 3 倍的示波器(如 16Gbps 信号需 48GHz 示波器),配合差分探头(输入阻抗 100Ω,带宽≥30GHz)。测试步骤包括:信号接入(使用探针或测试点)、触发设置(边沿触发或时钟恢复)、参数调整(时基设置为 UI 的 2-5 倍)和统计分析(至少采集 1000 个 UI)。关键参数解读:眼高应大于芯片最小输入摆幅的 80%,眼宽应大于数据手册要求的建立 / 保持时间总和,交叉点偏移应控制在 0.5UI±10% 以内。

时域反射计(TDR)测试用于定位阻抗不连续点。TDR 通过向传输线注入阶跃信号(典型上升时间 50ps),根据反射波形判断阻抗变化:正反射表示阻抗增大,负反射表示阻抗减小。在实际测试中,可通过 TDR 定位以下问题:连接器阻抗突变(通常会产生 10-30Ω 的阻抗跳变)、过孔寄生电感导致的阻抗尖峰、布线拐角引起的阻抗变化(直角拐角约增加 5-10Ω)。结合 TDT(时域传输)测试,还可分析传输线的插入损耗和时延特性,为仿真模型校准提供实测数据。

S 参数测量用于分析信号的频率特性。通过矢量网络分析仪(VNA)测量的 S11 参数反映回波损耗(与反射系数相关),S21 参数反映插入损耗(传输衰减)。对于高速背板设计,需关注以下指标:在信号奈奎斯特频率处,S11 应小于 - 15dB(反射较小),S21 插入损耗应大于 - 6dB(衰减可控)。差分信号还需测量 Sdd21(差分传输损耗)和 Scc21(共模抑制比),良好设计的差分对 Scc21 应比 Sdd21 低 20dB 以上,表明共模噪声抑制良好。

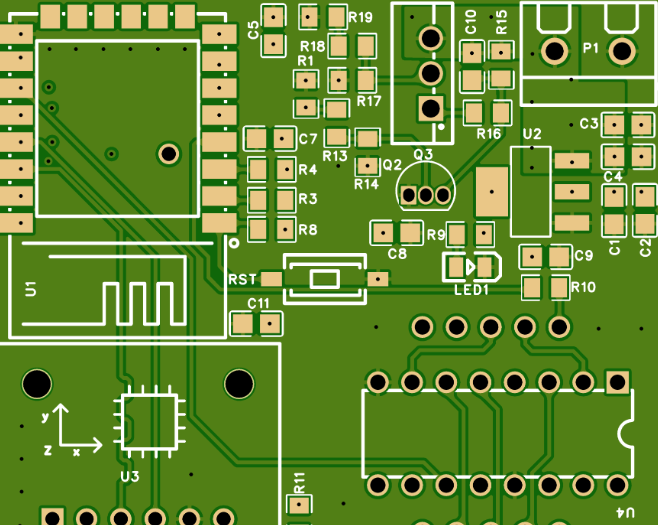

测试点设计直接影响测量准确性。高速信号的测试点应采用接地共面结构,避免信号反射;测试点与信号线的连接应采用渐变过渡,减少阻抗突变。探针着陆点直径建议≥10mil,相邻测试点间距≥50mil,防止探针间干扰。对于差分对测试,两个信号测试点间距应等于差分线间距,确保探头夹具的良好匹配。测试前需进行校准,包括:开路校准(去除探针寄生电容)、短路校准(去除探针寄生电感)和负载校准(确保阻抗参考准确)。

测试数据与仿真结果的对比分析至关重要。当两者存在偏差时(如实际眼高比仿真低 20%),需从三方面排查:仿真模型(是否低估了损耗)、测试 setup(是否引入额外噪声)和 PCB 制造(线宽、介质厚度是否在公差范围内)。通过迭代优化模型参数,可逐步缩小仿真与实测的差距,最终使关键指标偏差控制在 10% 以内,为后续设计积累准确的模型库。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号