盾罩接地孔密度计算在PCB屏蔽中到底有多大用?

在高速PCB设计中,电磁干扰(EMI)与信号完整性(SI)的矛盾日益突出。本文将深入解析接地孔密度计算模型,提供从理论到实践的优化方案。

一、盾罩接地孔的屏蔽机理与失效根源

盾罩接地孔通过形成连续的导电通路,将电磁干扰能量导入大地。其效能取决于三个核心参数:

电流密度分布:高频电流在孔壁的趋肤效应导致电流集中,密度超过5A/mm2时易引发局部过热

接地阻抗:孔间距过大(>5mm)会导致阻抗突变,形成二次辐射源

场耦合效应:未覆盖区域的电场强度与孔密度呈指数衰减关系(E∝e^(-λd),λ为衰减系数)

二、密度计算模型与关键参数

1. 基于FEM的电磁场仿真模型

采用ANSYS HFSS建立三维模型,重点关注:

孔径与间距比:推荐d/D=0.2-0.3(d为孔径,D为孔间距),可降低边缘场强30%

层叠结构影响:四层板接地孔密度需比双层板高40%以补偿返回路径阻抗

材料参数:FR4的相对磁导率μr=4.5时,孔密度需增加25%补偿损耗

2. 工程化计算公式

N = \frac{2\pi \mu_0 \sigma L}{V_{rms}^2} \cdot \ln(\frac{D}{d})

N:单位面积接地孔数量(孔/cm2)

\mu_0:真空磁导率(4π×10?? H/m)

\sigma:铜箔电导率(5.8×10? S/m)

L:特征长度(推荐取板厚1/2)

V_{rms}:允许的峰值电压(通常取5V)

D:孔间距,d:孔径

三、优化策略与实战技巧

1. 密度分级设计

核心区(CPU/射频模块):密度≥5孔/cm2,孔径0.8-1.2mm

过渡区(接口电路):密度3-4孔/cm2,孔径1.0-1.5mm

边缘区:密度≥2孔/cm2,采用锯齿形分布阻断爬电路径

2. 布局拓扑优化

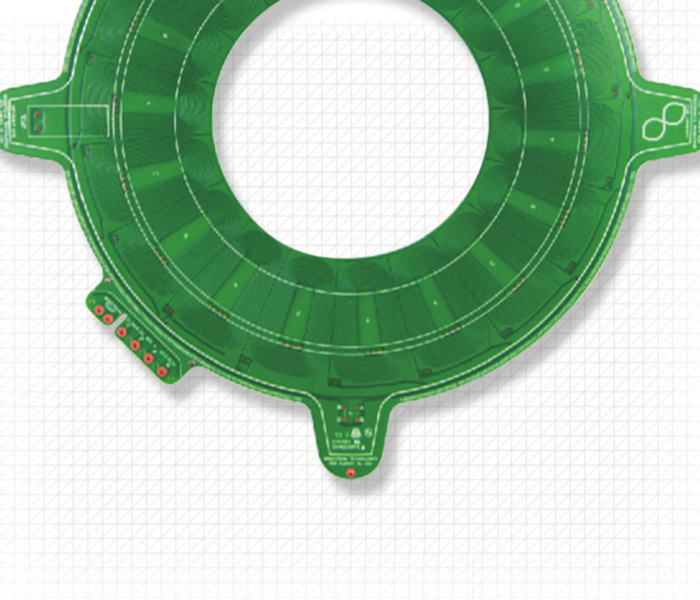

蜂窝阵列:六边形排列使电流分布均匀性提升25%

环形屏蔽墙:在敏感区域(如DDR4接口)设置同心圆孔阵,抑制共模辐射

动态密度调节:根据SIwave仿真结果,在电流密度>3A/mm2区域加密孔位

3. 工艺协同设计

激光盲孔:0.1mm孔径可使密度提升300%,但需控制孔深/孔径比<0.8

化学沉铜:采用黑孔工艺使孔壁粗糙度Ra<0.5μm,降低接触电阻

局部电镀:在高频区域使用脉冲电镀,铜厚增加50%提升载流能力

四、测试验证与迭代优化

1. 近场探头扫描法

使用100kHz-3GHz探头定位热点区域

设置阈值(>5dBμV/m)触发自动补孔算法

2. 多物理场联合仿真

电磁-热耦合仿真:预测高密度下的温升效应(ΔT<10℃为安全阈值)

振动可靠性测试:5Grms振动下孔位偏移量需<0.05mm

盾罩接地孔密度设计是电磁兼容领域的“黄金分割点”,需要平衡电性能、工艺成本与可靠性。通过建立精准的数学模型、采用分级布局策略、结合多物理场仿真,工程师可构建坚不可摧的电磁防线。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号