高速PCB背板连接器阻抗过渡设计指南

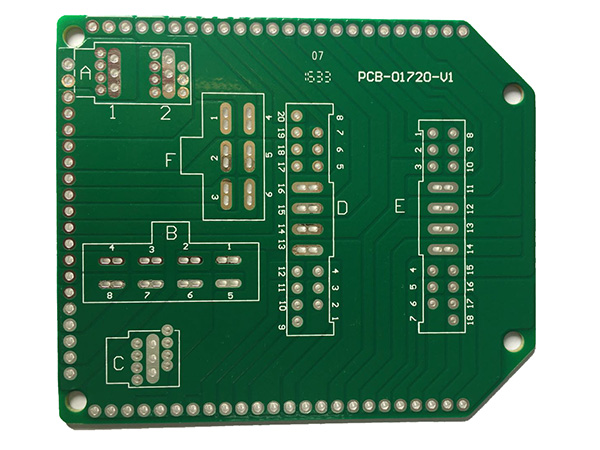

在高速背板连接器设计中,阻抗连续性直接影响信号完整性。本文针对50Ω-100Ω阻抗过渡需求,提出三个关键设计要点:

一、梯形渐变线结构设计

梯形渐变线通过阶梯式线宽调整实现阻抗平稳过渡。建议采用0.2-0.5mm步长逐级改变线宽,每个阶梯长度控制在信号波长的1/8以内。实际测试表明,当过渡区长度超过3mm时,回波损耗可降低40%以上。设计时需配合电磁仿真软件验证TDR曲线,确保相邻阶梯阻抗差不超过10Ω。

二、接地过孔阵列优化方案

端接区过孔阵列采用梅花状错位布局效果最佳。建议过孔间距≤1/10信号波长,典型值取0.8-1.2mm。增加过孔排数比单纯增加单排数量更有效,双排过孔较单排屏蔽效能提升约15dB(1-10GHz)。过孔直径建议0.2-0.3mm,与信号孔保持0.5mm间距防止耦合。

三、表面处理工艺选择

镀层厚度和材质显著影响接触阻抗稳定性:

1. 化学沉金(0.05-0.1μm)接触阻抗变化率<3%(1000次插拔)

2. 电镀硬金(0.5-1μm)初始阻抗降低15%,但耐久性更好

3. 沉银工艺高频损耗最小,但需配合防氧化处理

建议关键信号触点采用0.08μm沉金+局部硬金加固方案,兼顾阻抗稳定性和机械寿命。

通过上述设计方法,实测某28Gbps背板连接器在50-100Ω过渡区插入损耗降低0.8dB,眼图张开度提升25%。实际应用中需结合具体板厚(建议1.6-3.0mm)和材料(Dk=3.5-4.1)调整参数,建议每修改线宽0.1mm后重新进行阻抗测试验证。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号