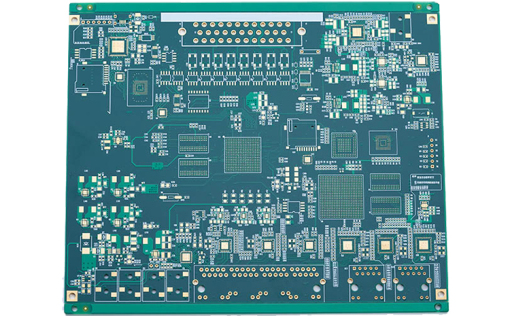

PCB层数优化设计与实现方法

PCB层数优化直接影响电路性能、成本和可靠性。以下从设计原则、结构布局、工艺适配三方面总结关键优化方法:

一、明确层数选择依据

信号复杂度与密度

? 简单电路(如低频控制板)可采用4层结构(信号-地-电源-信号),高频或高密度布线需增加层数至6层以上。? BGA封装器件密集区域需单独设置信号层,避免过孔过多导致布线受限。

电磁兼容性(EMC)要求

? 敏感信号层(如模拟电路)需与电源层相邻,中间插入地平面隔离干扰。? 高频信号(>5GHz)建议采用带状线结构,参考平面间距≤4mil。

成本与工艺限制

? 奇数层PCB需额外工艺处理,成本比偶数层高15%-20%,优先选择对称层数(如4/6/8层)。

二、叠层结构优化策略

电源与地平面布局

? 电源层与地层相邻,间距≤3mil以增强耦合电容(典型值0.5nF/cm2)。? 多电源层需分割区域,相邻信号层避免跨分割布线。

信号层分配规则

? 高速信号(如DDR4)优先布设于内层带状线,避免表层直连。? 相邻信号层走线方向正交(如X/Y轴交替),减少串扰。

对称性设计

? 铜厚镜像对称:例如顶层1oz、中间层3oz、底层1oz,降低热应力形变风险。? 介质厚度公差控制在±5%(阻抗层)以内,使用低收缩率半固化片(如1080)。

三、布线与制造适配

阻抗控制方法

? 带状线阻抗公式:Z?=87/√(Er+1.41)×ln(5.98H/(0.8W+T)),需匹配目标值±3%。? 差分线宽厚比建议5:1(如W=5mil、S=1mil),过孔间距≤20mil。

工艺参数优化

? 厚铜板(≥3oz)采用阶梯蚀刻:先蚀刻至2oz,二次图形化至目标厚度。? 混合材料叠层(如Rogers+FR4)需对称位置使用同膨胀系数基材。

可制造性验证

? TMA测试:热膨胀系数差异≤15ppm/℃,300mm板长翘曲≤0.75%。? 阻抗一致性测试:TDR采样点数≥板边接点数的20%。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号