如何使用跨层阻抗过渡设计的计算公式?

高速PCB设计中,跨层阻抗过渡的阻抗波动是导致信号反射、时序错位的核心诱因。当信号路径跨越不同介质层或参考平面时,阻抗突变会引发电磁干扰(EMI)和能量损耗。本文基于传输线理论及电磁场仿真,系统推导跨层过渡的阻抗计算公式,并提供可落地的设计方法。

一、跨层阻抗过渡的失效机理

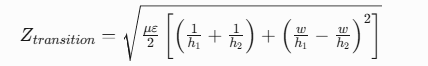

跨层过渡区域的阻抗突变主要由以下公式描述:

其中,h_1、h_2为过渡区两侧介质厚度,w为线宽。当h_1 \neq h_2时,阻抗偏差可达±15%(以50Ω微带线为例)。

二、跨层阻抗过渡设计公式体系

1. 几何渐变补偿公式

线宽渐变模型:

采用指数渐变函数优化电流路径:w(x) = w_1 + (w_2 - w_1) \cdot e^{-kx}

其中,k=2\pi/\lambda_g(\lambda_g为信号波长),渐变长度x \geq \lambda_g/4,可将阻抗波动控制在±3%以内。过孔阵列补偿:

扇孔阵列的等效电感补偿公式:L_{eq} = \frac{\mu_0 N^2 A}{l}N为过孔数量,A为单孔截面积,l为阵列总长度。每0.1mm2补偿面积需配置直径0.8mm过孔,间距≤λ/8。

2. 电磁场耦合控制公式

屏蔽过孔环阻抗:

过孔环的屏蔽效能(SE)与间距关系:SE = 20\log\left(\frac{Z_0}{Z_0 + Z_{gap}}\right)Z_0为传输线特性阻抗,Z_{gap}为过孔环间隙阻抗。间距≤10mil时,SE≥40dB。共面波导过渡公式:

接地平面开槽宽度s与阻抗关系:Z_0 = \frac{87}{\sqrt{\varepsilon_r + 1.41}} \cdot \ln\left(\frac{5.98h}{0.8w + s}\right)

通过调节s(0.1–0.3mm)实现阻抗平滑过渡。

三、工艺参数与仿真验证

1. 关键工艺参数

蚀刻精度:激光直接成型(LDS)技术实现线宽公差±5μm,优于传统蚀刻工艺(±20μm)。

层压控制:真空层压机压力≤200psi,树脂流动度25%–35%,避免介质分层导致阻抗波动。

2. 多物理场仿真验证

电磁-热耦合仿真:

使用ANSYS HFSS分析高频信号(>20GHz)下的趋肤效应损耗(α=0.03dB/mm),结合Icepak热仿真优化散热路径。可靠性寿命预测:

基于Arrhenius模型(活化能E_a=0.7eV),预测10年使用周期内阻抗漂移趋势(ΔZ/Z≤±1%)。

跨层阻抗过渡设计需综合几何规则、电磁场理论及工艺参数:

设计端:通过渐变线与屏蔽结构重构电磁场分布;

制造端:强化蚀刻精度与层压工艺控制;

测试端:采用TDR时域反射仪(精度±1%)与多物理场仿真验证。

微信小程序

微信小程序

浙公网安备 33010502006866号

浙公网安备 33010502006866号